# Current-Mode High Sensitivity CMOS Hall Magnetic Sensors

A Ph.D. Thesis by Hadi Heidari

Advisor:

Prof. Franco Maloberti

Integrated Microsystems Lab (IMS)

University of Pavia 2015 – XXVII

### **Thesis Oral Defense Examination Committee**

Professor Franco Maloberti, Fellow IEEE, University of Pavia

Professor Rinaldo Castello, Fellow IEEE, University of Pavia

Professor Valerio Re, University of Bergamo

Dr. Andrea Bevilacqua, University of Padova

To

my parents, brothers, sisters and my wife

#### Acknowledgements

I would like to begin this section by expressing my deepest and most sincere thank to Professor Franco Maloberti, head of our laboratory of Integrated Microsystems (IMS), for providing me the chance to explore such an intriguing yet challenging fields of the design of micro sensors. His great knowledge and guidance during the past three years benefit me greatly, not only arousing my interest in the study and research on microelectronics, but also nurturing my habit and ability to think in an independent manner. I am very thankful and honoured for that.

I would also like to express my gratitude to Dr. Edoardo Bonizzoni for his valuable advices and availability during the work on the projects. I gratefully acknowledge Dr. Umberto Gatti for numerous fruitful discussions we had, as well as for his support. A special thanks to Professor Piero Malcovati who rescues me from insolvable layout problems. I am also thankful to the my colleagues at University of Macau (UM), specially Kameng Lei, Professor Pui-In Mak and Professor Matthew Man-Kay Law for helping me through the Vertical Magnetic Sensor projects and their supporting for fabrication of prototypes and PCBs.

There are few people during my PhD who participated kindly and scientifically to help and encourage me, namely: Athanasios Kiouseloglou, Erika Covi and Kambiz Hadipour. Thanks guys, having such great friends make me happy life.

A big thanks to my colleagues and friends at IMS lab who helped me and who made my time at the work more enjoyable. Particularly, Marco Grassi, Yao Liu, Aldo Peña Perez, Alessandro Cabrini, Da Feng, Dante Gabriel Muratore and Reza Bagh. Many thanks to the people in Pavia whom i shared many good moments, Specially, Sanaz Kianoush, Junlei Zhao, Lorenzo Ferrara, Raniero Covi, Rodrigo Ferreira, Mydia Freitas, Vijayakumar Rajamanickam and Assel Yerbassova.

My infinite gratitude to my family who love me unconditionally. I would never complete my study successfully without their support. I thank my brothers and sisters and especially my parents, who shaped my personality and supported me.

Finally, I would thank my wife Sara, who has stood by me through this whole process, reminding me to celebrate the good times and giving me the strength to endure the difficult ones.

## **Contents**

| Intr | oductio                                                                                                  | n                                                                                                                                                                                                                                                                                                               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1  | Motiva                                                                                                   | ation and Objectives                                                                                                                                                                                                                                                                                            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1.2  | Thesis                                                                                                   | Overview and Summary of Results                                                                                                                                                                                                                                                                                 | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Refe | erences .                                                                                                |                                                                                                                                                                                                                                                                                                                 | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Hall | Magne                                                                                                    | etic Sensors                                                                                                                                                                                                                                                                                                    | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2.1  | The H                                                                                                    | all Effect                                                                                                                                                                                                                                                                                                      | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2.2  | Hall E                                                                                                   | ffect Devices                                                                                                                                                                                                                                                                                                   | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 2.2.1                                                                                                    | Geometry                                                                                                                                                                                                                                                                                                        | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 2.2.2                                                                                                    | Material                                                                                                                                                                                                                                                                                                        | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2.3  | Horizo                                                                                                   | ontal vs. Vertical CMOS Hall Devices                                                                                                                                                                                                                                                                            | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.4  | Currer                                                                                                   | nt-Mode vs. Voltage-Mode Technique                                                                                                                                                                                                                                                                              | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.5  | Magne                                                                                                    | etic Sensors Characteristics                                                                                                                                                                                                                                                                                    | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | 2.5.1                                                                                                    | Sensitivity                                                                                                                                                                                                                                                                                                     | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | 2.5.2                                                                                                    | Offset                                                                                                                                                                                                                                                                                                          | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | 2.5.3                                                                                                    | Noise                                                                                                                                                                                                                                                                                                           | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | 2.5.4                                                                                                    | NonLinearity                                                                                                                                                                                                                                                                                                    | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.6  | State-o                                                                                                  |                                                                                                                                                                                                                                                                                                                 | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | 2.6.1                                                                                                    | Sensitivity Improvement                                                                                                                                                                                                                                                                                         | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | 2.6.2                                                                                                    | Offset Reduction                                                                                                                                                                                                                                                                                                | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.7  | Applic                                                                                                   |                                                                                                                                                                                                                                                                                                                 | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Refe |                                                                                                          |                                                                                                                                                                                                                                                                                                                 | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Cur  | rent-M                                                                                                   | ode Horizontal Hall Magnetic Sensors                                                                                                                                                                                                                                                                            | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      |                                                                                                          | •                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      |                                                                                                          |                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| ٥.2  | _                                                                                                        |                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | 0.2.1                                                                                                    |                                                                                                                                                                                                                                                                                                                 | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      |                                                                                                          |                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3 3  |                                                                                                          |                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      |                                                                                                          | ation and Picasticinent Results                                                                                                                                                                                                                                                                                 | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | 1.1<br>1.2<br>Refe<br>Hall<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>Refe<br>Cur<br>3.1<br>3.2 | 1.1 Motiva<br>1.2 Thesis<br>References<br>Hall Magne<br>2.1 The H<br>2.2 Hall E<br>2.2.1<br>2.2.2<br>2.3 Horizo<br>2.4 Currer<br>2.5 Magne<br>2.5.1<br>2.5.2<br>2.5.3<br>2.5.4<br>2.6 State-o<br>2.6.1<br>2.6.2<br>2.7 Applic<br>References<br>Current-M<br>3.1 Propos<br>3.2 Imples<br>3.2.1<br>3.2.2<br>3.2.3 | 1.1 Motivation and Objectives 1.2 Thesis Overview and Summary of Results References  Hall Magnetic Sensors 2.1 The Hall Effect 2.2 Hall Effect Devices 2.2.1 Geometry 2.2.2 Material 2.3 Horizontal vs. Vertical CMOS Hall Devices 2.4 Current-Mode vs. Voltage-Mode Technique 2.5 Magnetic Sensors Characteristics 2.5.1 Sensitivity 2.5.2 Offset 2.5.3 Noise 2.5.4 NonLinearity 2.6 State-of-the-art in CMOS Hall Magnetic Sensors 2.6.1 Sensitivity Improvement 2.6.2 Offset Reduction 2.7 Applications of Hall Magnetic Sensors References  Current-Mode Horizontal Hall Magnetic Sensors 3.1 Proposed Architecture 3.2 Implementation 3.2.1 Horizontal Current-Mode Hall Sensor Devices 3.2.2 Sensor Biasing Circuit 3.2.3 Current Spinning Switches 3.3 Simulation and Measurement Results |

xii Contents

| 4 | Cur   | rent-Mode Vertical Hall Magnetic Sensors 53                   |

|---|-------|---------------------------------------------------------------|

|   | 4.1   | Proposed Architecture                                         |

|   | 4.2   | Implementation                                                |

|   |       | 4.2.1 Four-Folded Vertical Sensor Device                      |

|   |       | 4.2.2 Offset Reduction                                        |

|   |       | 4.2.3 System Implementation                                   |

|   | 4.3   | Simulation and Modeling                                       |

|   | 4.4   | Measurement Results                                           |

|   | Refe  | erences                                                       |

| 5 | Mag   | gnetic Sensor Interface                                       |

|   | 5.1   | Analog Front-End                                              |

|   | 5.2   | Horizontal Prototype                                          |

|   |       | 5.2.1 Readout Circuit                                         |

|   |       | 5.2.2 Digital Control Unit and Output Switched-Capacitor (SC) |

|   |       | Filter 78                                                     |

|   |       | 5.2.3 Measurement Results                                     |

|   | 5.3   | Vertical Prototype                                            |

|   |       | 5.3.1 Readout Circuit                                         |

|   |       | 5.3.2 Switches and Digital Control Unit                       |

|   |       | 5.3.3 Switched-Capacitor Filter                               |

|   |       | 5.3.4 Measurement Results                                     |

|   | Refe  | erences                                                       |

| 6 | Con   | <b>clusions</b>                                               |

|   | 6.1   | Highlights                                                    |

|   | 6.2   | Outlook                                                       |

| A | Lay   | out Description                                               |

|   | A.1   | First Chip Layout Description (PVHALLREADOUT) 104             |

|   | A.2   | Second Chip Layout Description (PVVHSSENSORS)                 |

|   | A.3   | Third Chip Layout Description (PVVHSREADOUT)                  |

| В | Hall  | Effect Model Considerations in COMSOL Multiphysics 109        |

|   | Refe  | erences                                                       |

| C | I ict | of Publication 115                                            |

# **List of Figures**

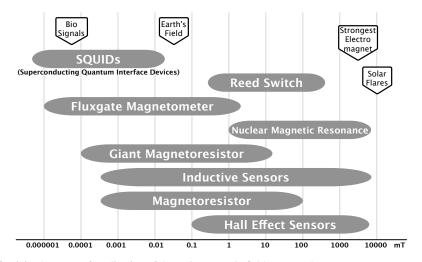

| 1.1   | The range of application of the main magnetic field sensors [4]                                                                                                                                         | 2  |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

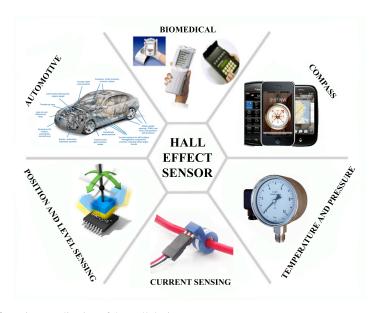

| 1.2   | Various application of the Hall devices                                                                                                                                                                 | 3  |

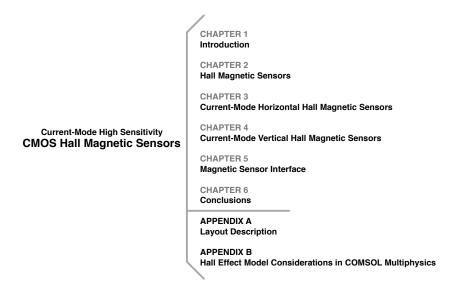

| 1.3   | Thesis structure.                                                                                                                                                                                       | 5  |

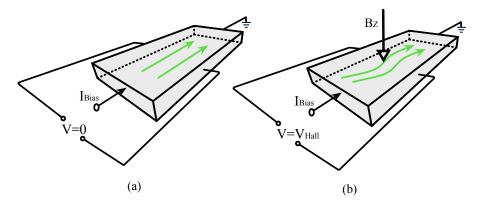

| 2.1   | A rectangle Hall plate in presence of (a) no magnetic field and (b) a perpendicular magnetic field $(B_z)$                                                                                              | 8  |

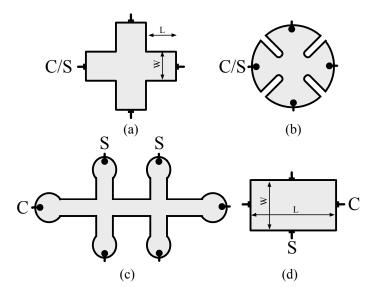

| 2.2   | Various shapes of Hall plates: (a) Cross-shaped, (b) Van der Paw shape, (c) Bridge shape and (d) Rectangle shape. C are the current contacts, S the sense contacts and C/S indicates that the two types |    |

| 2.3   | of contacts are interchangeable [2]                                                                                                                                                                     | 9  |

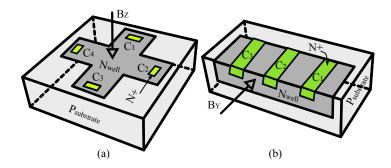

| 2.4   | device cross-sections in CMOS technology                                                                                                                                                                | 11 |

| ∠.∓   | 6-contact (6C) vertical Hall devices in CMOS technology                                                                                                                                                 | 11 |

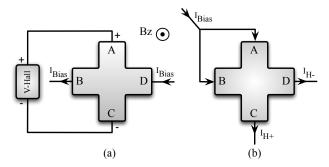

| 2.5   | (a) Hall plate operating in voltage-mode. (b) Hall plate working in current-mode.                                                                                                                       | 12 |

| 2.6   | Wheatstone bridge model of cross-shape Hall sensor in (a)                                                                                                                                               |    |

|       | voltage-mode and (b) current-mode configuration                                                                                                                                                         | 16 |

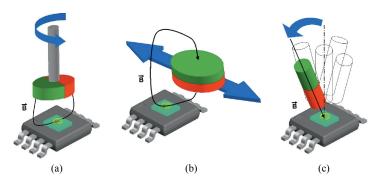

| 2.7   | (a) Orthogonal coupling of two cross-shaped Hall plates. (b) The                                                                                                                                        |    |

|       | biasing and sensing are altered using the symmetry of the Hall                                                                                                                                          |    |

|       | plate. (c) The current spinning technique: the biasing and sensing contacts are switched periodically in order to modulate either the                                                                   |    |

|       | Hall voltage or the offset [9].                                                                                                                                                                         | 17 |

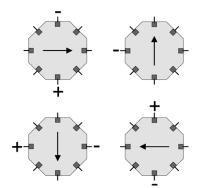

| 2.8   | (a) Applying the current spinning technique to 4-contact and (b)                                                                                                                                        |    |

|       | 8-contact horizontal Hall sensors (reprinted from [32] and [28])                                                                                                                                        | 18 |

| 2.9   | Four phases of a quad current spinning Hall plate for reduce the                                                                                                                                        |    |

|       | offset (reprinted from [7])                                                                                                                                                                             | 19 |

| 2.10  | Spinning-current technique applying to 5-contact vertical Hall                                                                                                                                          | •  |

| 0 1 1 | sensor (reprinted from [31]).                                                                                                                                                                           | 20 |

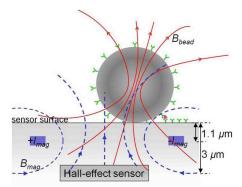

| 2.11  | Cross section of a label detector using CMOS magnetic Hall sensor                                                                                                                                       | 24 |

|       | (reprinted from [17])                                                                                                                                                                                   | 24 |

xiv List of Figures

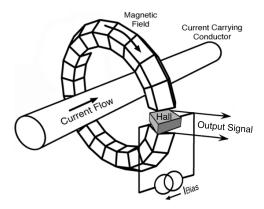

|      | Basic configuration of a contactless current Hall effect sensor             | 25 |

|------|-----------------------------------------------------------------------------|----|

|      | (reprinted from [1]).                                                       | 26 |

| 2.14 | Entire IMC structure and Hall plates (reprinted from [41])                  | 26 |

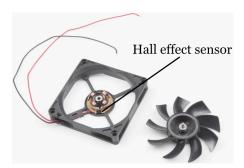

|      | DC brushless fan using Hall effect sensor.                                  | 27 |

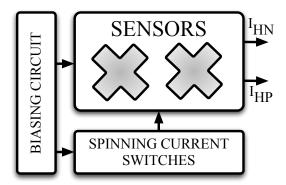

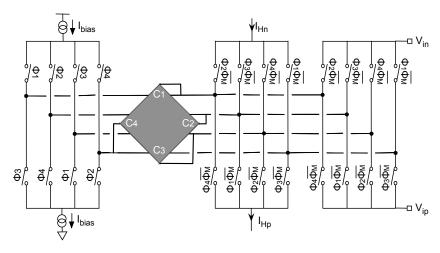

| 3.1  | Block diagram of the proposed magnetic current-mode Hall sensor             | 32 |

| 3.2  | Spinning current technique and output offset of a single                    |    |

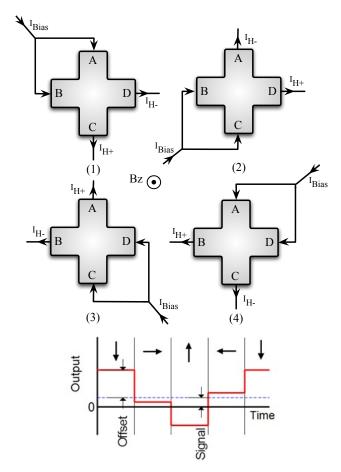

|      | cross-shaped Hall plate during four states                                  | 33 |

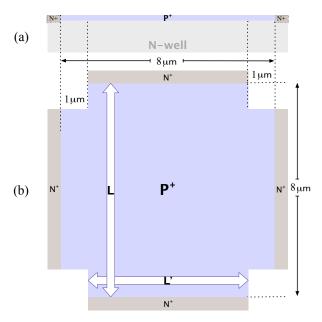

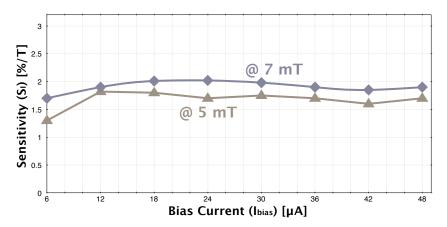

| 3.3  | Model geometry of a cross-shaped Hall plate in a CMOS                       |    |

|      | technology: (a) cross view and (b) top view                                 | 34 |

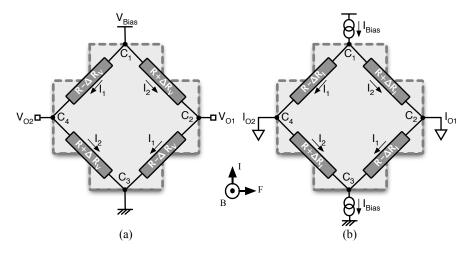

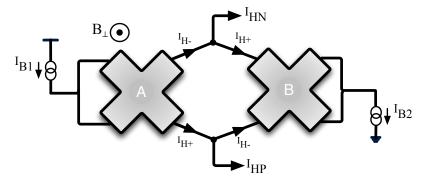

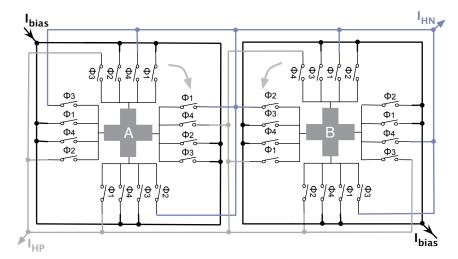

| 3.4  | Proposed twin current-mode Hall sensor structure                            | 35 |

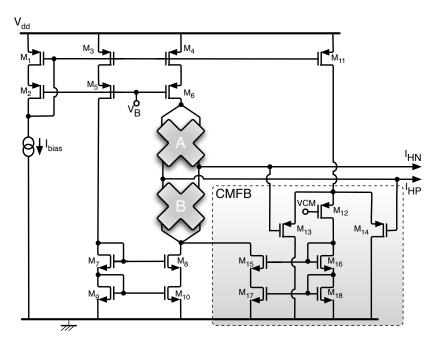

| 3.5  | Schematic diagram of Hall plates with biasing and common mode               |    |

|      | feedback circuit.                                                           | 36 |

| 3.6  | Hall plates with switches configuration for current spinning                | 38 |

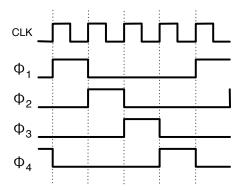

| 3.7  | Phases timing diagram for current spinning operation                        | 38 |

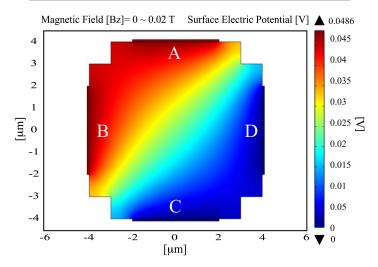

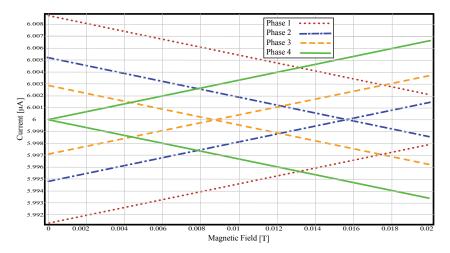

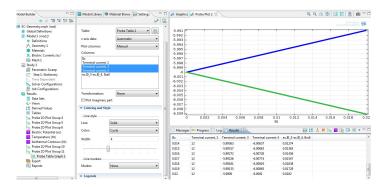

| 3.8  | COMSOL simulation results of a single current-mode cross-shaped             |    |

|      | Hall sensor.                                                                | 39 |

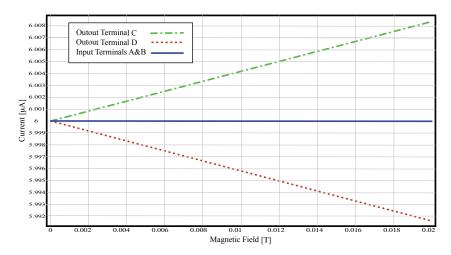

| 3.9  | Simulated input and output currents of the current-mode Hall plate          |    |

|      | without any mismatch                                                        | 39 |

| 3.10 | Simulated average output currents ( $I_{H+}$ and $I_{H-}$ ) of current-mode |    |

|      | Hall sensor plate with mismatch after the current spinning method           | 41 |

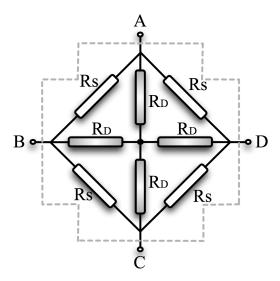

|      | The 8-resistors model implemented in Verilog-A using eight resistors.       | 41 |

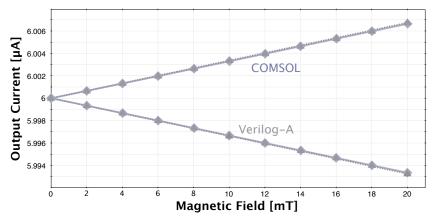

| 3.12 | Simulated output currents of the Hall plate in COMSOL and                   |    |

|      | Verilog-A as a function of magnetic field                                   | 42 |

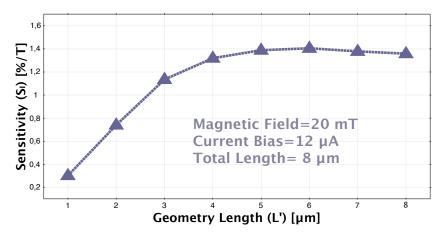

|      | Simulated sensitivity as a function of the Hall plate width                 | 43 |

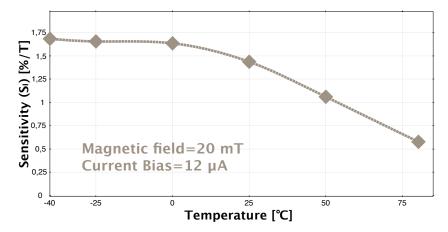

|      | Simulated sensitivity as a function of the temperature                      | 44 |

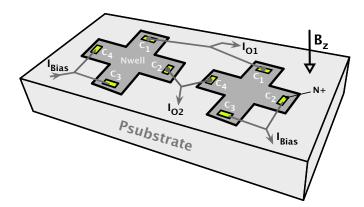

|      | Twin horizontal current-mode Hall device in CMOS technology                 | 44 |

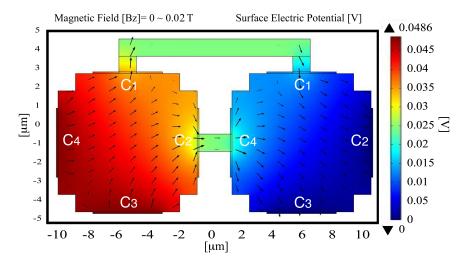

| 3.16 | COMSOL simulation results of a twin current-mode cross-shaped               |    |

|      | Hall sensor.                                                                | 45 |

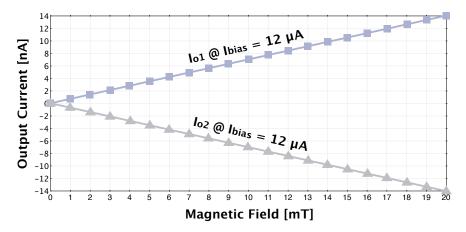

| 3.17 | Simulated output currents ( $I_{O1}$ and $I_{O2}$ ) of a cross-shaped       |    |

|      | current-mode horizontal Hall sensor as a function of the magnetic           |    |

|      | field at 12 µA bias current                                                 | 45 |

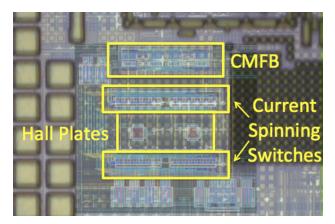

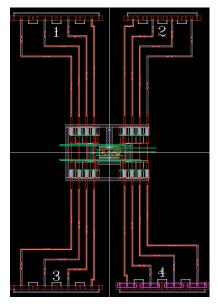

|      | Chip microphotograph of the most relevant blocks                            | 46 |

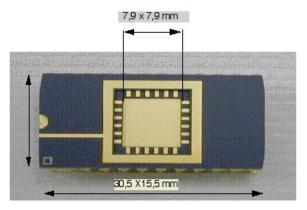

|      | Dual in-line 24-pins package of fabricated chip                             | 46 |

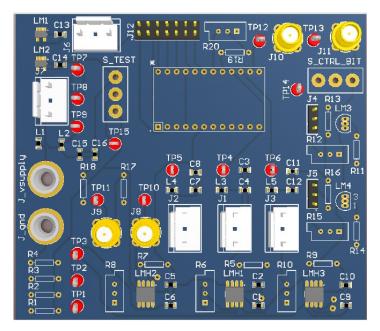

|      | 3D Top layer of the BCB board test in Altium                                | 47 |

|      | Fabricated 2-layers test board with soldered components                     | 48 |

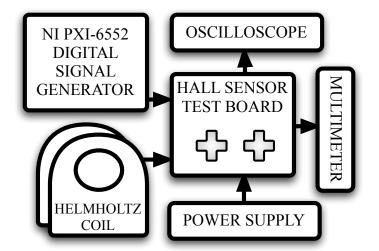

|      | Used measurement setup                                                      | 48 |

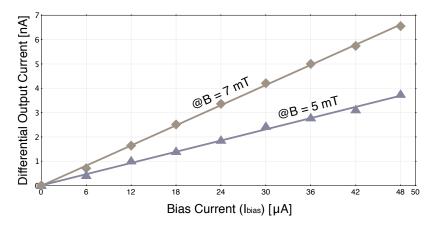

| 3.23 | Measured sensor output current as a function of the biasing current         |    |

|      | at different magnetic fields.                                               | 49 |

| 3.24 | Measured sensor sensitivity as a function of the biasing current at         |    |

|      | different magnetic fields.                                                  | 49 |

List of Figures xv

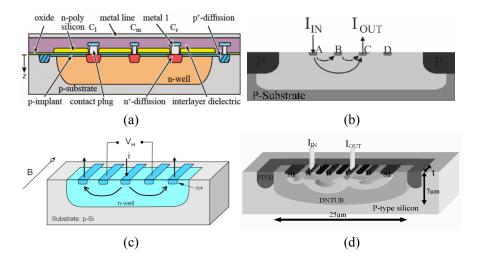

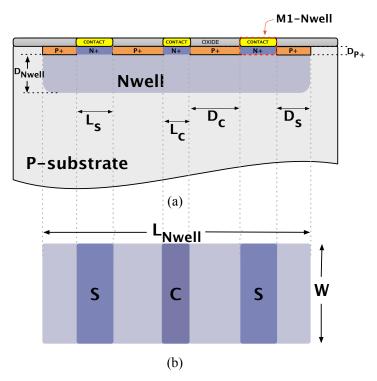

| 4.1        | The 3-contact vertical Hall sensor in semiconductor substrate of a                                                                      |    |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.2        | CMOS technology: (a) cross section view and (b) top view                                                                                | 55 |

|            | (b) vertical Hall device in voltage-mode, (c) vertical Hall device in current-mode configuration: biasing conditions and currents flows | 57 |

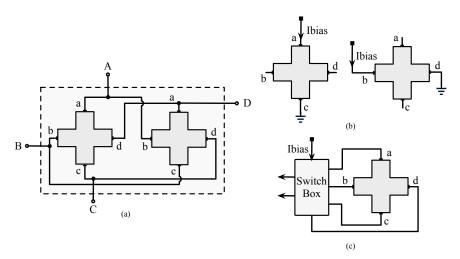

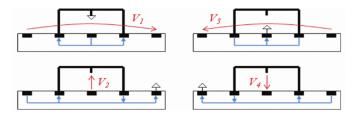

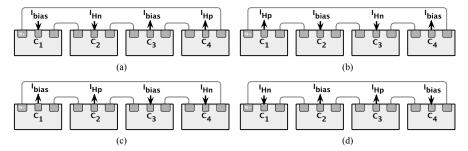

| 4.3        | The four modes current spinning configuration: (a) Mode 1, (b)                                                                          | 51 |

|            | Mode 2, (c) Mode 3 and (d) Mode 4 for a 4-folded 3-contact                                                                              |    |

|            | vertical Hall sensor                                                                                                                    | 58 |

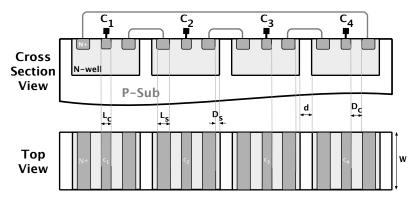

| 4.4        | The 4-folded 3-contact vertical Hall sensor in cross section view                                                                       |    |

|            | and top view.                                                                                                                           | 59 |

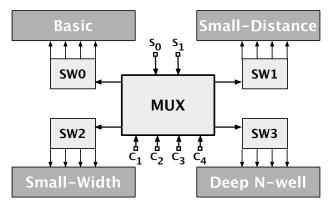

| 4.5        | Placement of four analyzed Hall devices on a tested chip                                                                                | 60 |

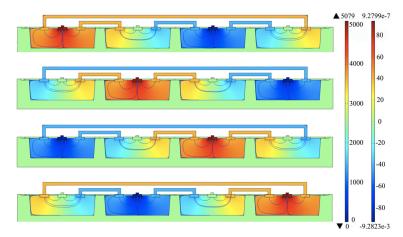

| 4.6        | Simulation of three contact vertical Hall device in COMSOL                                                                              |    |

|            | environment and current streamline of four modes of operating in                                                                        |    |

|            | the current-mode.                                                                                                                       | 61 |

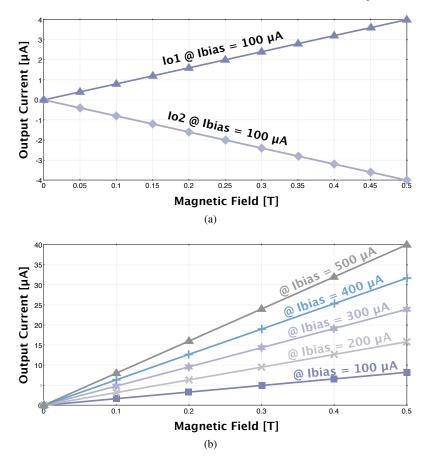

| 4.7        | (a) Simulated sensor output currents as a function of the magnetic                                                                      |    |

|            | field at 100 μA bias current after four phases, and (b) Simulated                                                                       |    |

|            | sensor Hall current as a function of the different biasing current at                                                                   | 62 |

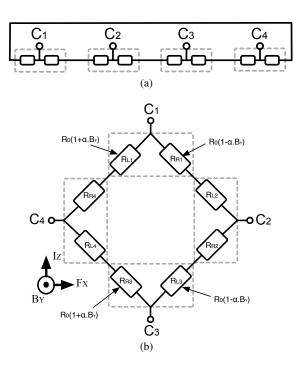

| 4.8        | different magnetic field                                                                                                                | 02 |

| 4.0        | resistors, (b) A same model in a Wheatstone bridge depiction                                                                            | 63 |

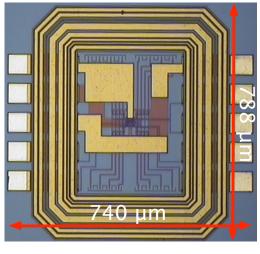

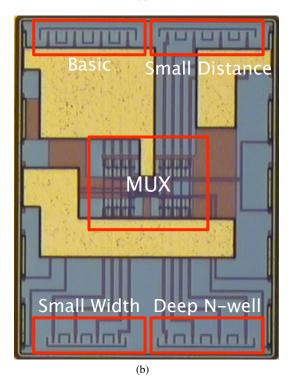

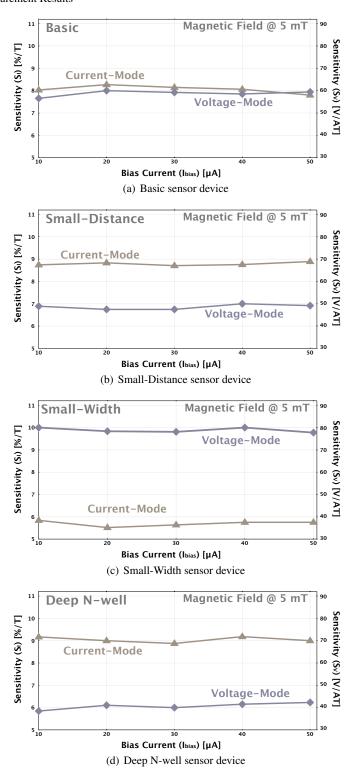

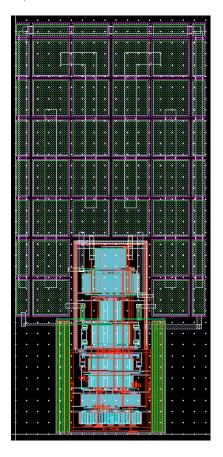

| 4.9        | (a) PVVHSSENSOR chip microphotograph, (b) placement of the                                                                              | U. |

| т.)        | multi-sensors on the same chip                                                                                                          | 66 |

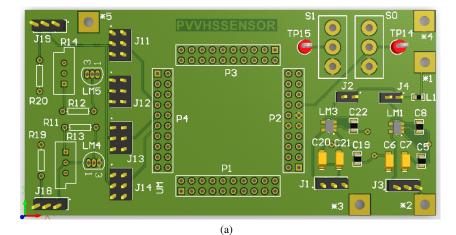

| 4.10       | (a) 3D Top layer of the BCB board test in Altium, (b) fabricated                                                                        |    |

|            | test board with components soldered.                                                                                                    | 67 |

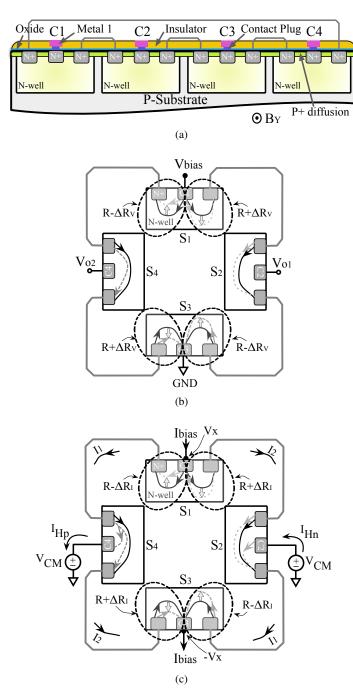

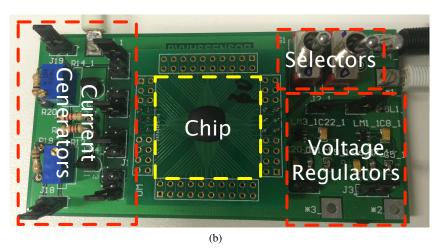

| 4.11       | Configuration of the fabricated chip in (a) Voltage-mode and (b)                                                                        |    |

|            | Current-mode                                                                                                                            | 68 |

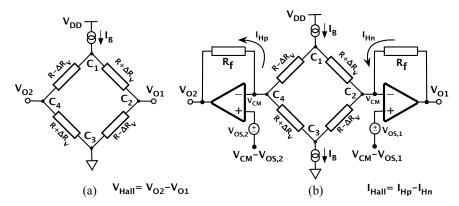

| 4.12       | Measured sensitivity of each vertical Hall sensor as a function of                                                                      |    |

|            | bias current in both current and voltage modes                                                                                          | 69 |

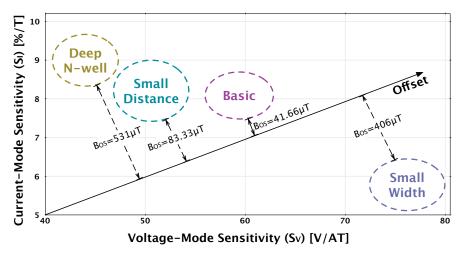

| 4.13       | Comparison of four different geometries of vertical Hall sensors                                                                        |    |

|            | in terms of current-mode sensitivity, voltage-mode sensitivity and                                                                      |    |

|            | magnetic field equivalent offset.                                                                                                       | 70 |

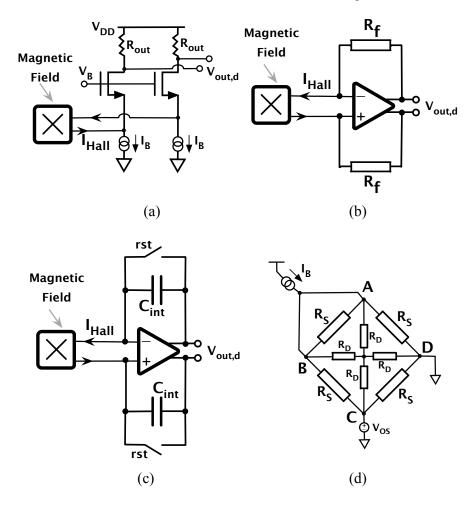

| 5.1        | Three I/V configurations: (a) common-gate detection, (b) resistive                                                                      |    |

|            | detection and (c) integrator capacitive detection. (d) 8-resistors Hall                                                                 |    |

|            | plate equivalent model                                                                                                                  | 74 |

| 5.2        | Block diagram of the proposed horizontal magnetic current-mode                                                                          |    |

|            | Hall sensor microsystem                                                                                                                 | 75 |

| 5.3        | Analog front-end; (a) top-level architecture of current-to-voltage                                                                      |    |

|            | converter and (b) its two stage fully differential amplifier                                                                            | 77 |

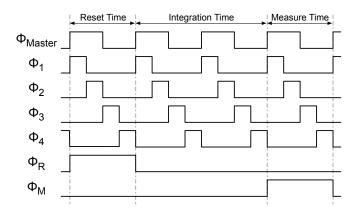

| 5.4        | Phases timing diagram for current spinning, reset and measure                                                                           |    |

|            | operation                                                                                                                               | 78 |

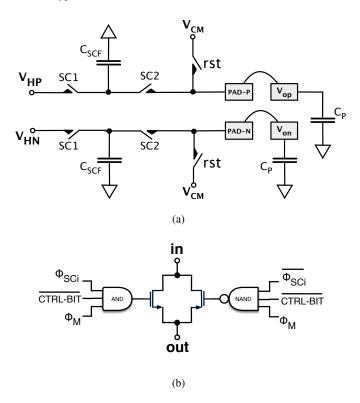

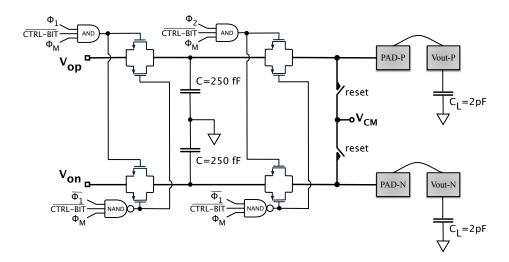

| 5.5        | Output stage of the sensor system; (a) Switched-capacitor filter and                                                                    |    |

| <b>-</b> - | (b) phase control of its complementary CMOS switches                                                                                    | 79 |

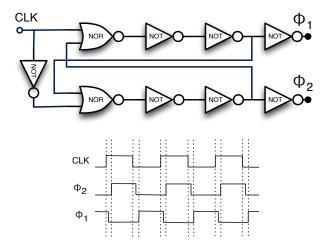

| 5.6        | Implemented non-overlapping phase generator                                                                                             | 80 |

xvi List of Figures

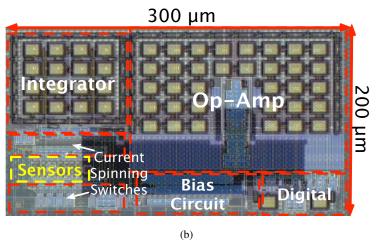

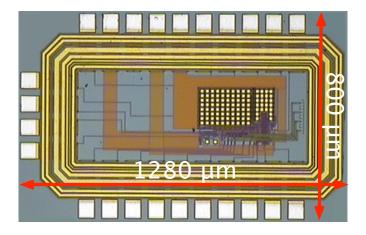

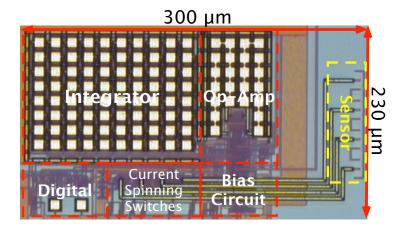

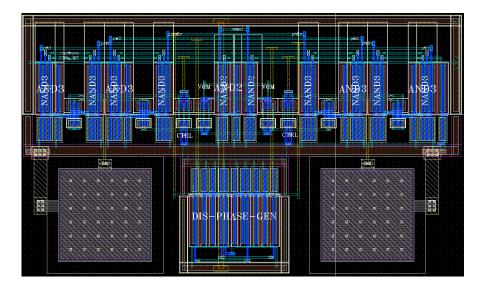

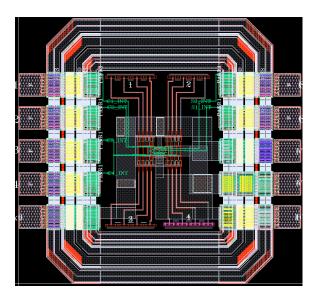

| 5.7                 | Hall sensor microphotograph: (a) whole chip including pads with                                                                    | 0.1 |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------|-----|

| <b>7</b> 0          | (b) its back-annotated layout of main circuital blocks                                                                             | 81  |

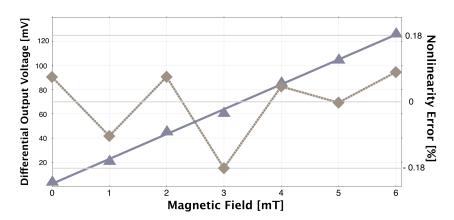

| 5.8                 | Measured sensor differential output voltages as function of the                                                                    | 0.0 |

| <b>7</b> 0          | magnetic field and its nonlinearity error.                                                                                         | 82  |

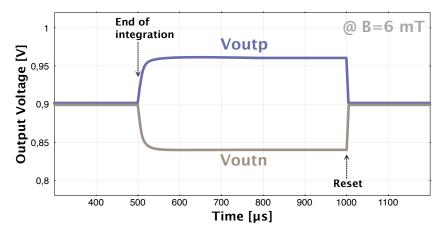

| 5.9                 | Measured transient response of output voltages.                                                                                    | 84  |

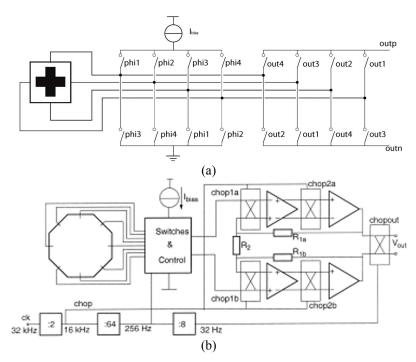

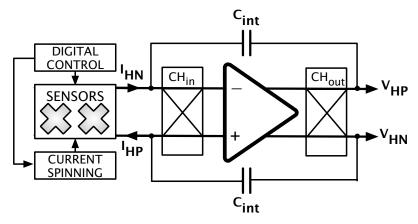

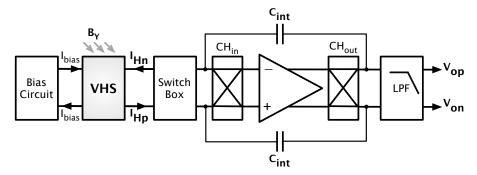

|                     | Block diagram of proposed vertical current-mode Hall microsystem.                                                                  | 84  |

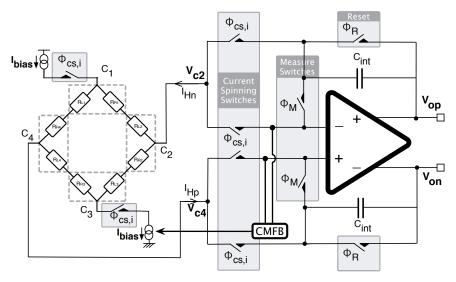

|                     | Overall scheme of vertical Hall microsystem configuration                                                                          | 85  |

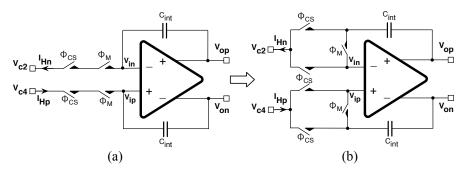

| 5.12                | Proposed placement of measure switches, $\Phi_M$ , for cancelling of                                                               | 0.0 |

| 5 12                | voltage drop across it.                                                                                                            | 86  |

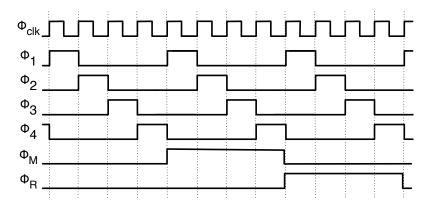

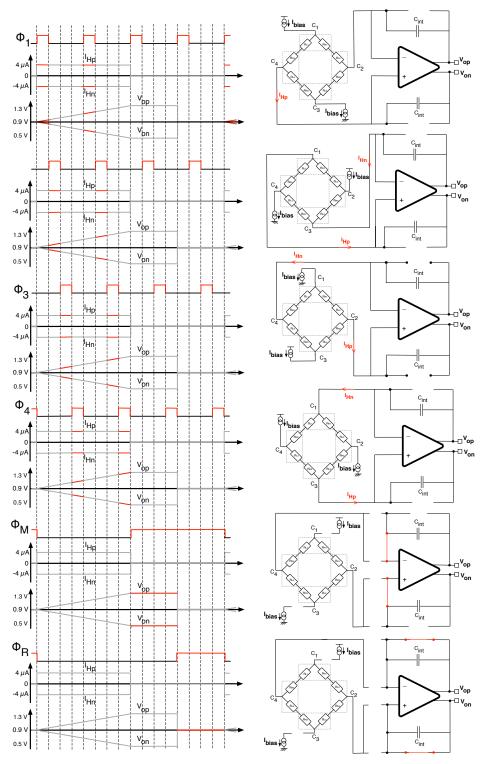

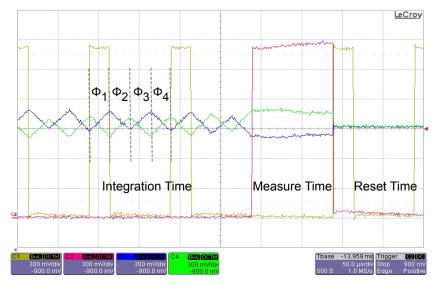

| 5.13                | Vertical Hall microsystem operations of driving phases                                                                             | 0.0 |

| <i>5</i> 1 <i>1</i> | $\Phi_1, \Phi_2, \Phi_3, \Phi_4, \Phi_M \text{ and } \Phi_R.$                                                                      | 88  |

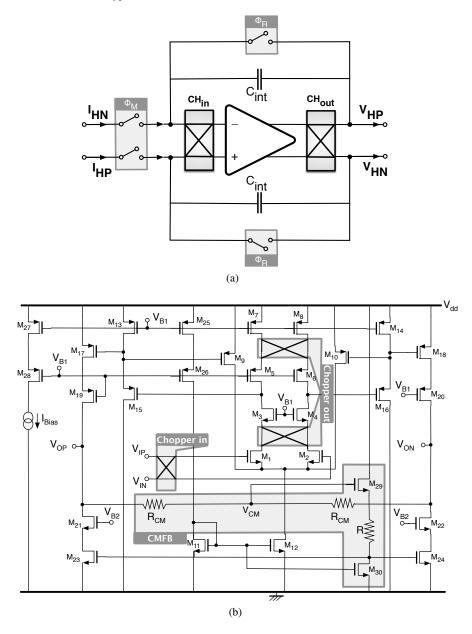

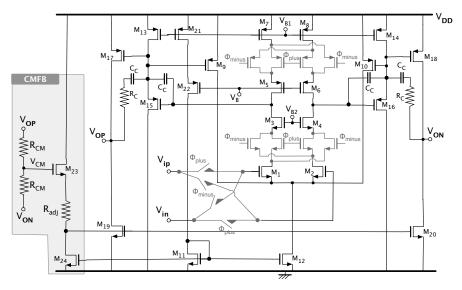

| 5.14                | Circuit schematic of used op-amp in analog interface of vertical                                                                   | 0.0 |

| <i>5 15</i>         | Hall sensor.                                                                                                                       | 89  |

| 3.13                | Implementation of the four-phase current spinning technique for                                                                    | 00  |

| 5 16                | the vertical Hall sensor.                                                                                                          | 90  |

| 3.10                | Diagram and timing sequence of the six-phases for controlling of                                                                   | 90  |

| 5 17                | the current spinning during integration, reset and measure time Proposed switched-capacitor filter as a output circuit of magnetic | 90  |

| 5.17                | Hall microsystem.                                                                                                                  | 91  |

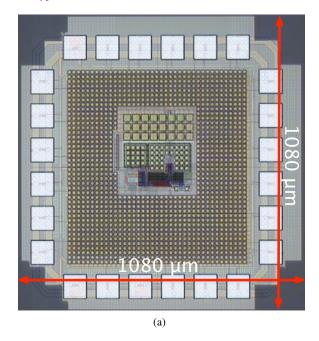

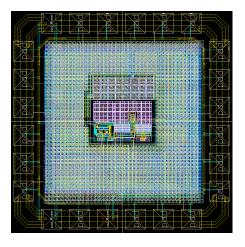

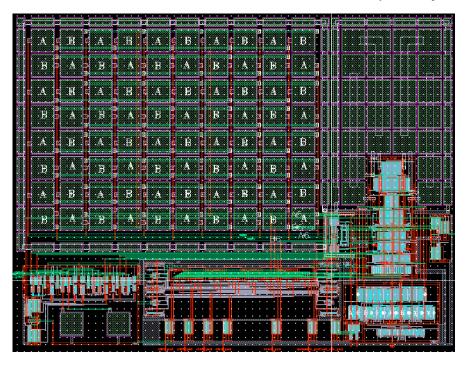

| 5 1 2               | PVVHSREADOUT chip microphotograph                                                                                                  | 92  |

|                     | Main circuital blocks of the vertical Hall sensor with integrated                                                                  | 72  |

| 3.19                | interface                                                                                                                          | 92  |

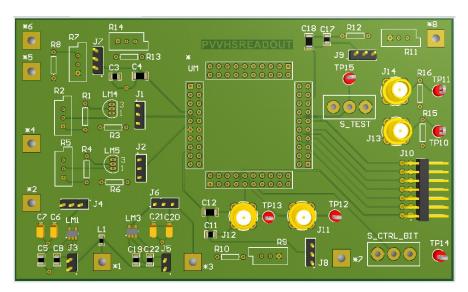

| 5 20                | 3D Top layer of the BCB board test in Altium.                                                                                      | 93  |

|                     | Fabricated test board with components soldered.                                                                                    | 93  |

|                     | Used measurement setup                                                                                                             | 94  |

|                     | Output Voltage transient response measured with active microprobe.                                                                 | 96  |

| 0.20                | output votage transfert response measured with delive interoproces.                                                                |     |

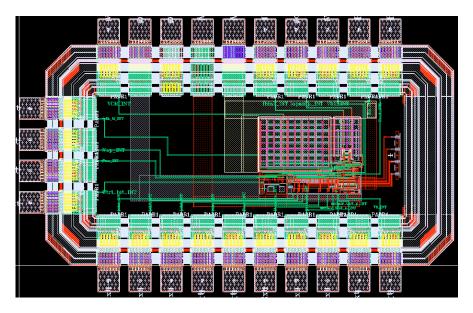

| A.1                 | Layout of the integrator readout interface including a fully                                                                       |     |

|                     | differential telescopic Op-Amp with discrete-time CMFB                                                                             | 04  |

| A.2                 | Switched-capacitor filter layout including a non-overlapping phase                                                                 |     |

|                     | generator for chopper phases and other digital parts                                                                               | 04  |

| A.3                 | Sensor plate layout including four metal1 to N <sup>+</sup> high doped                                                             |     |

|                     | contacts and a low doped N-well, which is covered by a shallow                                                                     |     |

|                     | highly doped P <sup>+</sup> 1                                                                                                      | 05  |

| A.4                 | Full view of the layout chip core including the op-amp, the digital                                                                |     |

|                     | control unit, the bias and the current spinning switches                                                                           | 05  |

| A.5                 | Top view layout of whole horizontal Hall sensor including pad-ring                                                                 |     |

|                     | and density filled                                                                                                                 | 05  |

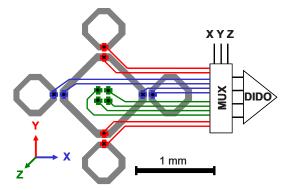

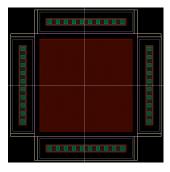

| A.6                 | Layout of chip core including a multiplexer with four different                                                                    |     |

|                     | vertical Hall sensor                                                                                                               |     |

| A.7                 | Top view layout of vertical Hall sensor including the pad-ring 1                                                                   | 06  |

| A.8                 | Layout of the fully differential telescopic Op-Amp with                                                                            |     |

|                     | discrete-time CMFB                                                                                                                 | 07  |

| A.9                 | Switch box includes 32 switches for the implementation of the                                                                      |     |

|                     | current spinning technique                                                                                                         | 07  |

List of Figures xvii

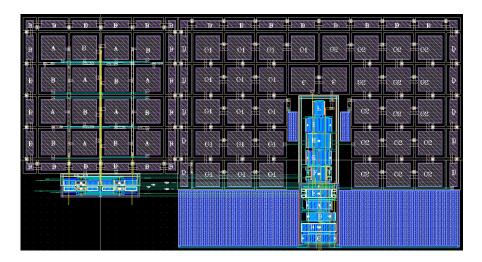

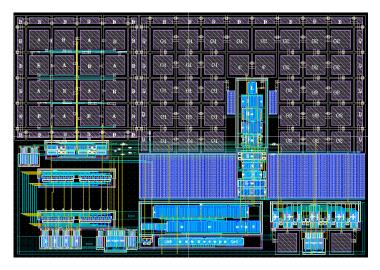

| A.10 | Core layout of vertical Hall sensor including switched-capacitor   |       |

|------|--------------------------------------------------------------------|-------|

|      | filter, analog readout circuit, digital parts and current spinning |       |

|      | switches without pad-ring                                          | . 108 |

| A.11 | Top view layout of vertical Hall sensor with analog front-end and  |       |

|      | its padring                                                        | . 108 |

| D 4  | W 112                                                              | 400   |

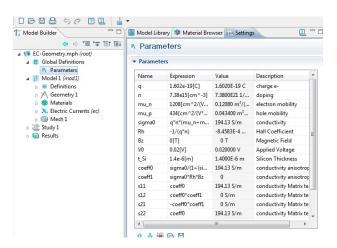

|      | Model Parameters                                                   |       |

| B.2  | Model Geometry                                                     | . 110 |

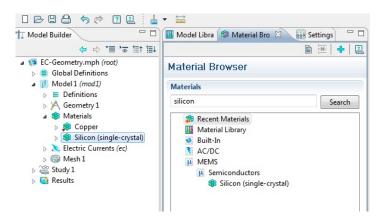

| B.3  | Model Materials                                                    | . 110 |

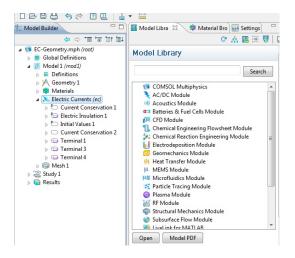

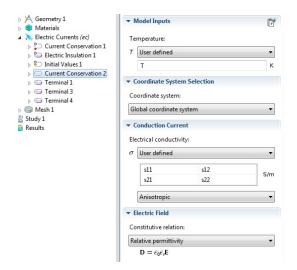

| B.4  | Model physics                                                      | . 111 |

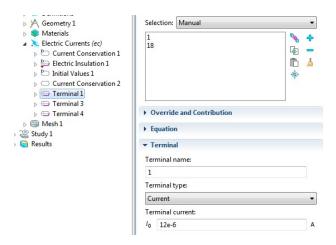

| B.5  | Model physics                                                      | . 111 |

| B.6  | Model physics                                                      | . 112 |

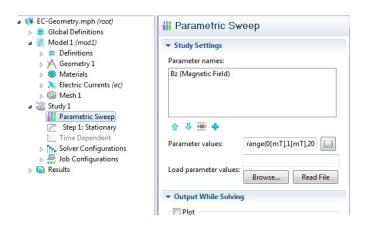

| B.7  | Model Study                                                        | . 112 |

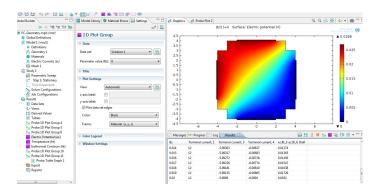

| B.8  | 2D plot electric potential result                                  | . 113 |

| B.9  | 1D plot graph result.                                              | . 113 |

## **List of Tables**

| 1.1 | Research Target                                                           | 4  |

|-----|---------------------------------------------------------------------------|----|

| 2.1 | Gap and mobility of semiconductors at 300 K used to build a Hall          |    |

| 2.2 | plate [6] Sensitivity of Horizontal Hall Magnetic Sensors in Voltage-Mode | 10 |

| 2.2 | and Current-Mode conditions                                               | 15 |

| 2.3 | Sensitivity Comparison of Horizontal and Vertical Hall Magnetic           |    |

|     | Sensors                                                                   | 22 |

| 2.4 | Offset Comparison of Horizontal and Vertical Hall Magnetic Sensors        | 23 |

| 3.1 | Four phases for spinning current method                                   | 34 |

| 3.2 | Model Parameters                                                          | 39 |

| 3.3 | Simulation results of the current-mode Hall plate without mismatch        | 40 |

| 3.4 | Comparison between the simulations of the Hall plate in COMSOL            |    |

|     | and Verilog-A                                                             | 42 |

| 3.5 | Performance Summary                                                       | 50 |

| 4.1 | Geometry variations of four different integrated 4-folded 3-contact       |    |

|     | vertical Hall sensors                                                     | 59 |

| 4.2 | Model Parameters of a 2D VHS Model in COMSOL                              | 61 |

| 4.3 | Numerical comparison between the simulations of the vertical Hall         |    |

|     | device in COMSOL and Verilog-A                                            | 64 |

| 4.4 | Integrated four different vertical Hall sensors characterization          | 70 |

| 5.1 | Hall Microsystem Performance Summary                                      | 82 |

| 5.2 | Comparison table of this work with other state-of-the-art horizontal      |    |

|     | CMOS Hall sensors                                                         | 83 |

| 53  | PVVHSRF ADOLIT Microsystem Performance Summary                            | 95 |

# Acronyms

Flicker Noise

1/f

| 1/1           | FIICKEI INOISE                                    |

|---------------|---------------------------------------------------|

| 3D            | Three Dimensional                                 |

| ABS           | Anti-lock Braking system                          |

| ADC           | Analog to Digital Converter                       |

| AMR           | Anisotropic Magneto-Resistance                    |

| ASIC          | Application Specific Integrated Circuit           |

| CAD           | Computer Aided Design                             |

| CAGR          | Compound Annual Growth Rate                       |

| CM            | Current-Mode                                      |

| CMFB          | Common Mode FeedBack                              |

| CMOS          | Complementary Metal Oxide Semiconductor           |

| CS            | Current Spinning                                  |

| DAC           | Digital to Analog Converter                       |

| FEM           | Finite Element Modeling                           |

| GBW           | Gain BandWidth                                    |

| GMR           | Giant Magneto-Resistance                          |

| IC            | Integrated Circuit                                |

| IVC (I/V      | ) Current to Voltage Converter                    |

| IMC           | Integrated Magnetic Concentrator                  |

| LPF           | Low Pass Filter                                   |

| <b>MEMS</b>   | Micro Electro Mechanical System                   |

| MOS           | Metal Oxide Semiconductor                         |

| MOSFET        | Metal Oxide Semiconductor Field-Effect Transistor |

| MUX           | Multiplexer                                       |

| NLE           | Non-Linearity Error                               |

| NMR           | Nuclear Magnetic Resonance                        |

| OpAmp         | Operational Amplifier                             |

| PCB           | Printed Circuit Board                             |

| PM            | Phase Margin                                      |

| RRL           | Ripple Reduction Loop                             |

| SCF           | Switched Capacitor Filter                         |

| SNR           | Signal to Noise Ratio                             |

| <b>SQUIDs</b> | Superconducting Quantum Interface Devices         |

| VCM           | Voltage Common Mode                               |

| VM            | Voltage Mode                                      |

| VHS           | Vertical Hall Sensor                              |

| VLSI          | Very Large Scale Integration                      |

|               |                                                   |

# Chapter 1 Introduction

**Abstract** The interest in magnetic sensors has significantly increased in recent years thanks to attractive advantages in various applications. In fact, magnetic sensors are more and more used not only for automotive and compass applications but also in a large variety of biomedical systems. This enormous popularity is the main driving force for the development of many state-of-the-art architectures with good trade-off between higher sensitivity, low offset and low power dissipation. Moreover, sensors may exhibit high residual offset due to the imperfections of their building blocks and can also result in a challenging system because it involves analog and digital issues for its study, design and implementation. This thesis focuses on the description of several solutions in current-mode situation for horizontal and vertical Hall magnetic sensors. All of the proposed architectures, supported by many simulation results with COMSOL Multiphysics, explore design strategies to reduce the offset and improve the sensitivity without affecting the overall performance of the sensors. Three prototypes have been integrated in a standard 0.18-um CMOS technology. The measurement results of these prototypes not only confirm the effectiveness of the sensors but also provide to the reader with a more general overview of the design strategies used to accomplish the major goal of this work: design for maximum sensitivity.

#### 1.1 Motivation and Objectives

Hundreds of millions of magnetic sensor devices are produced every year for use in a wide variety of applications [1]. The analysts forecast the Global Magnetic Sensors market to grow at a CAGR <sup>1</sup> of 7.21 percent over the period 2013-2018. One of the key factors contributing to this market growth is the increasing usage in automotive and electronic compasses. The Global Magnetic Sensors market has also been witnessing the miniaturization of magnetic sensors. However, the increasing cost of automotive systems could pose a challenge to the growth of this market [2].

<sup>&</sup>lt;sup>1</sup> Compound Annual Growth Rate

2 1 Introduction

Figure 1.1 presents the typical ranges of application of the main magnetic sensors and shows the role of Hall effect sensor between them. Very small magnetic fields, usually biomagnetic fields, are measured using SQUID (Superconducting Quantum Interface Devices) sensors. Above 0.1 nT, fluxgate sensors can be used. These are much smaller and detect the vector value. But in order to obtain the best parameters, it should be very carefully manufactured. In the range around the Earth's magnetic field, the anisotropic magnetoresistance (AMR) and giant magnetoresistivity (GMR) sensors are much cheaper. Inductive sensors (search coils), which can be used over a very wide range of values – from very small pT range to very large magnetic fields, from DC (when sensor is moved) to GHz bandwidth, exhibit special features [3].

Fig. 1.1 The range of application of the main magnetic field sensors [4].

Large magnetic field is almost exclusively measured by Hall effect sensors. Hall effect sensors have been the workhorse magnetic sensor for decades. Hall sensors are based on the Hall effect transduction principle and measure either constant or varying magnetic field. They have a magnetic field sensitivity range from tens of  $\mu T$  to more than 1 T and have a die size less than one millimetre. Their performance, size and low cost have made them the most popular type of magnetic devices. This is even more true since Hall sensors are easily integrated in modern commercial CMOS technologies.

Fig. 1.2 shows the diversity of Hall effect sensors applications. They are widely used in:

- Biomedical: Anesthesia delivery systems, sleep apnea machines, infusion, insulin or syringe pumps, dental equipment [5]

- Automotive: ignition timing, antilock braking systems (ABS), E-Valve actuators

- Computers: commutation for brushless fans, disk drive index sensors

- Industrial controls: temperature and pressure sensors, speed sensors, position and level sensing, current sensors

- Consumer Devices: exercise equipment, cell phones, compass.

Fig. 1.2 Various application of the Hall devices.

The motivation for this thesis work is to explore the features and limits of the current-mode Hall sensors in both horizontal and vertical method. In order to complete this study, three levels have been considered:

- 1. The sensor device level,

- 2. The analog front-end circuit level,

- 3. The system level topology with optimization of analog building blocks.

On the sensor device level, several shapes and geometries of sensor plates have been simulated and investigated. Between them the cross-shaped plate has been selected because of its symmetrically use of current spinning technique used for offset reduction. The model has been developed in current-mode for saving power and improving the sensitivity. The current-mode sensor has been simulated at first using COMSOL Multiphysics. After that the sensor device model has been then implemented in Verilog–A description language, for behavioural simulations in the Cadence environment.

On the analog front-end circuit level, the readout circuit consists of an Op-Amp that behaves like an integrator, the bias circuits of two Hall plates, current spinning switches and the common mode feedback (CMFB).

4 1 Introduction

On the system level, the novel topologies facilitated have been investigated by examining the features of the current-mode Hall sensors. This level focuses on system analysis, including considerations about overall noise, power consumption, sensitivity and offset. There is a trade-off between the number of sensor contacts and the residual offset of the sensor device.