## UNIVERSITA' DEGLI STUDI DI PAVIA FACOLTA' DI INGEGNERIA DOTTORATO DI RICERCA IN MICROELETTRONICA, XXIII CICLO

## CMOS CIRCUITS FOR SERIAL LINKS BEYOND 10Gb/s

Tutor: Chiar.mo Prof. Francesco Svelto

Ph. D. dissertation of Giorgio Spelgatti

# Index

| INDEX        |                                              |     |

|--------------|----------------------------------------------|-----|

| INTRODUCTION |                                              | . 7 |

| CHAPTER 1    |                                              |     |

| HIGH SPE     | ED SERIAL LINK                               | 9   |

| 1.1          | INTRODUCTION                                 | . 9 |

| 1.2          | BINARY CODING                                | 10  |

| 1.2.1        | NRZ data                                     | 10  |

| 1.2.2        | RZ data                                      | 12  |

| 1.2.3        | Generation of random data                    | 12  |

| 1.3          | Link overview                                | 14  |

| 1.3.1        | Link description                             | 14  |

| 1.3.2        | Serial channel link                          | 15  |

| 1.3.3        | Serial channel link standard                 | 17  |

| 1.3.4        | Serial optical link                          |     |

| 1.3.5        | Serial optical link standard                 | 20  |

| 1.4          | SYSTEM CHARACTERIZATION                      |     |

| 1.4.1        | Eye diagram                                  | 21  |

| 1.4.2        | Bit error ratio (BER)                        | 22  |

| 1.4.3        | Bathtub curves                               | 22  |

| 1.4.4        | Jitter tolerance                             | 23  |

| 1.5          | PERFORMANCES LIMITS                          | 24  |

| 1.5.1        | Intersymbol Interference (ISI)               | 24  |

| 1.5.2        | Noise                                        | 26  |

| 1.5.3        | Jitter                                       | 28  |

| 1.6          | ANALOG EQUALIZATION TECHNIQUES               | 29  |

| 1.6.1        | Introduction                                 |     |

| 1.6.2        | Linear equalizer                             | 29  |

| 1.6.3        | Decision Feedback equalizer (DFE)            | 31  |

| 1.6.4        | Loop-Unrolled digital DFE                    | 33  |

| 1.6.5        | Half-rate DFE with one tap of loop unrolling | 34  |

| 1.6.6        | Continuous time DFE (CTDFE)                  | 35  |

| 1.7          | DIGITAL EQUALIZATION TECHNIQUES              | 36  |

| 1.7.1        | Introduction                                 | 36  |

| 1.7.2        | Digital Feed-forward equalizer (FFE)         | 37  |

| 1.7.3        | VDA (Viterbi decoding algorithm)             | 38  |

| 1.8          | CDR TECHNIQUES                               | 39  |

| 1.8.1        | Introduction                                 | 39  |

| 1.8.2        | Linear PD (Hogge)                            | 39  |

| 1.8.3        | Bang bang PD (Alexander)                     | 40  |

| 1.8.4        | Mueller Muller PD                            | 42  |

| 1.8.5    | Clock generation (charge pump & VCO)                  | 43 |

|----------|-------------------------------------------------------|----|

| 1.8.6    | Clock generation (phase interpolator)                 | 44 |

| 1.9      | SUMMARY                                               | 46 |

| СНАРТЕБ  |                                                       | 47 |

| DIGITAL  | CIRCUITS FOR A 12GB/S RECEIVER                        | 47 |

| 2.1      | INTRODUCTION                                          | 47 |

| 2.2      | RECEIVER ARCHITECTURE                                 | 47 |

| 2.3      | BANG-BANG CDR                                         | 49 |

| 2.3.1    | Digital CDR                                           | 49 |

| 2.3.2    | Phase detector                                        | 49 |

| 2.3.3    | Loop Filter                                           | 51 |

| 2.3.4    | Signals of phase increment and decrement              | 52 |

| 2.3.5    | Clock phases generation                               | 53 |

| 2.3.6    |                                                       |    |

| 2.3.7    | Tracking of sinusoidal jitter                         | 56 |

| 2.4      | HORIZONTAL EYE OPENING MAXIMIZATION                   | 57 |

| 2.4.1    | Un-clocked DFE                                        | 57 |

| 2.4.2    | 0                                                     |    |

| 2.4.3    | Pattern-selective early late detector                 |    |

| 2.4.4    |                                                       |    |

| 2.5      | VERTICAL EYE OPENING MAXIMIZATION                     |    |

| 2.5.1    | 0 0 0                                                 |    |

| 2.5.2    | 6                                                     |    |

| 2.5.3    | 0 0                                                   |    |

| 2.6      | PRBS CHECKER                                          |    |

| 2.7      | INTERNAL EYE MONITOR                                  |    |

| 2.8      | DIE MICROGRAPH                                        |    |

| 2.9      | MEASUREMENTS RESULTS                                  |    |

| 2.9.1    |                                                       |    |

| 2.9.2    |                                                       |    |

| 2.9.3    |                                                       |    |

| 2.9.4    | Jitter tolerance (high frequency)                     |    |

| 2.10     | LITERATURE COMPARISON                                 |    |

| 2.11     | SUMMARY                                               |    |

| CHAPTER  | <b>{</b> 3                                            | 77 |

| DESIGN C | OF A 6BIT, 5GS/S FLASH ADC                            |    |

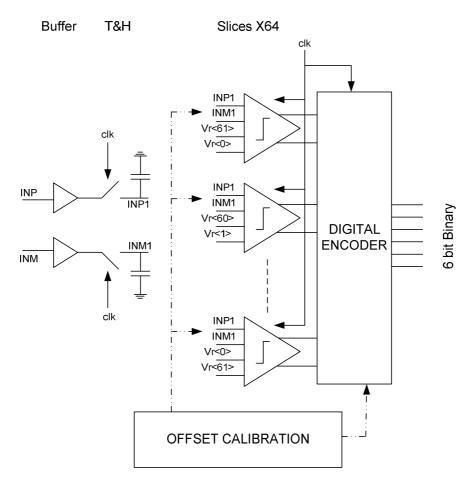

| 3.1      | INTRODUCTION                                          | 77 |

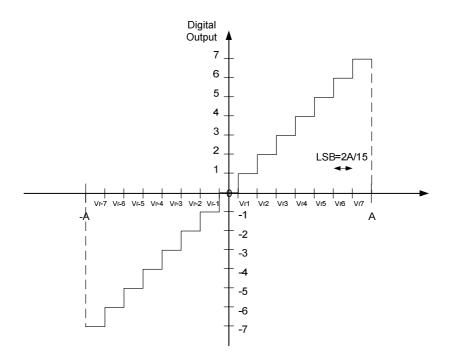

| 3.2      | ADC BASICS                                            | 77 |

| 3.2.1    | Basic operation                                       | 77 |

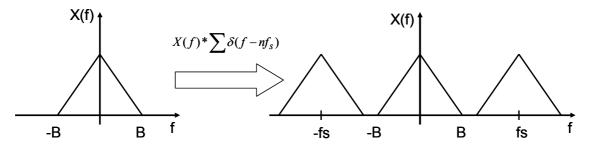

| 3.2.2    | Sampling                                              |    |

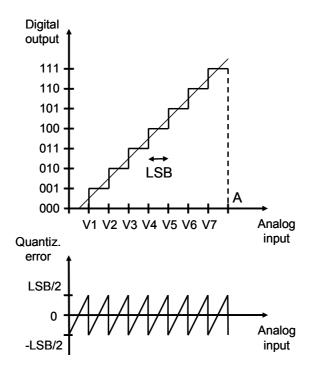

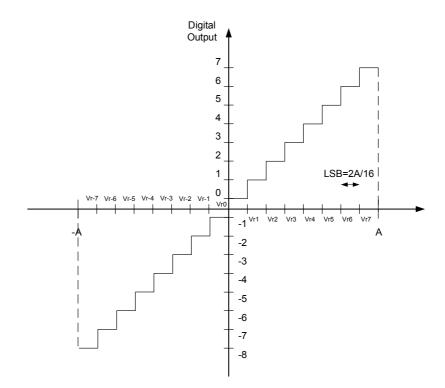

| 3.2.3    | Amplitude quantization and ADC specifications         | 79 |

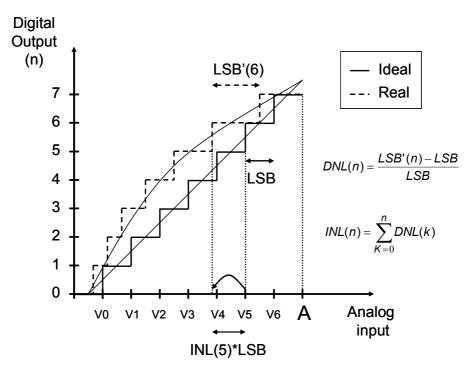

| 3.2.4    | Differential and integral non linearity (DNL & INL)   | 81 |

| 3.3      | FLASH ARCHITECTURE & CIRCUITS NON-IDEALITIES          | 82 |

| 3.3.1    | Flash architecture                                    |    |

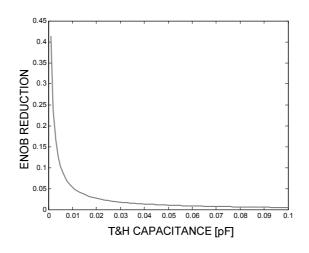

| 3.3.2    | Buffer and Track & Hold attenuation and non-linearity | 85 |

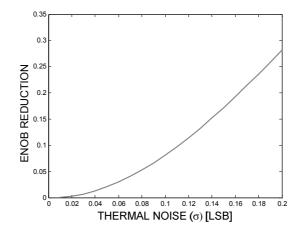

| 3.3.3        | Thermal noise                        |  |

|--------------|--------------------------------------|--|

| 3.3.4        | Slice resolution                     |  |

| 3.3.5        | Residual offset                      |  |

| 3.3.6        | Expected results                     |  |

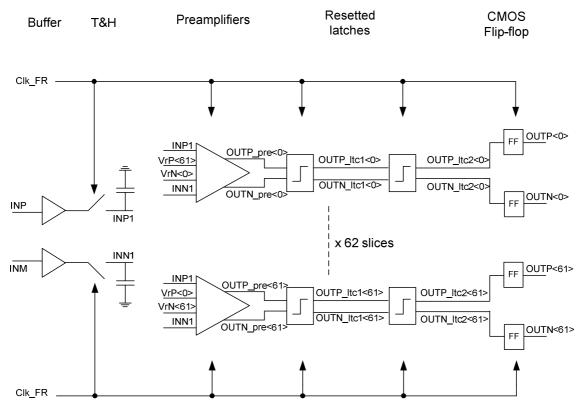

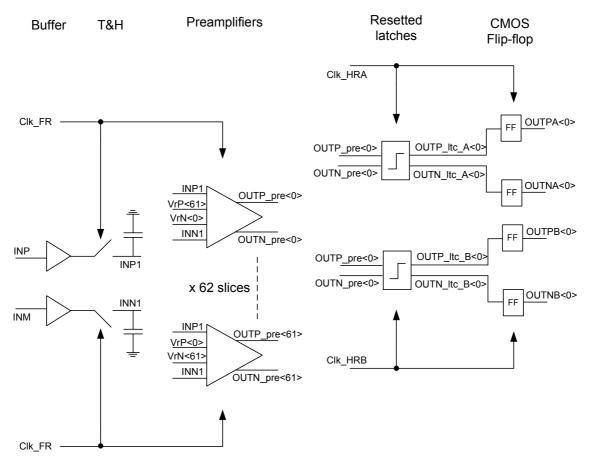

| 3.4          | FULL-RATE VS. HALF-RATE ARCHITECTURE |  |

| 3.4.1        | Introduction                         |  |

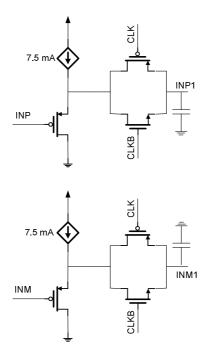

| 3.4.2        | Buffer and track & hold              |  |

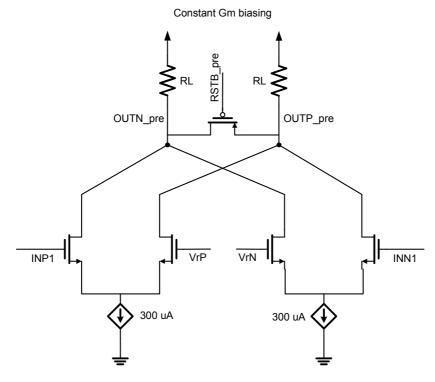

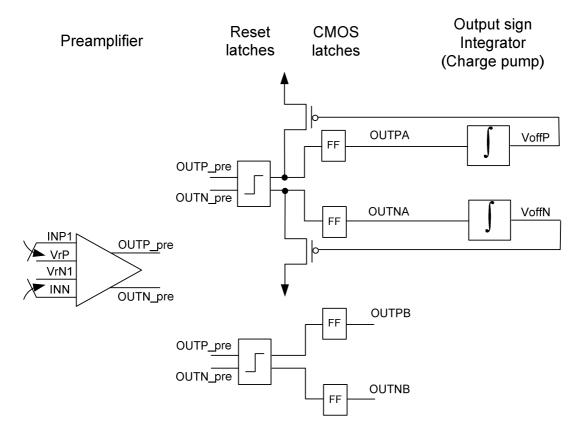

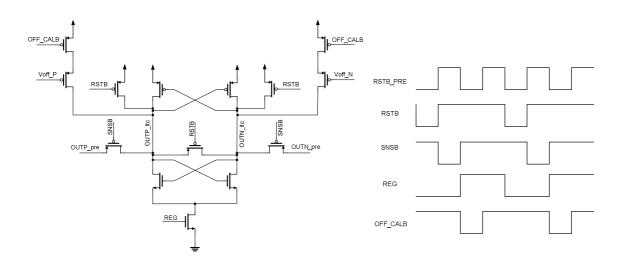

| 3.4.3        | Preamplifier                         |  |

| 3.4.4        | Full-rate latches                    |  |

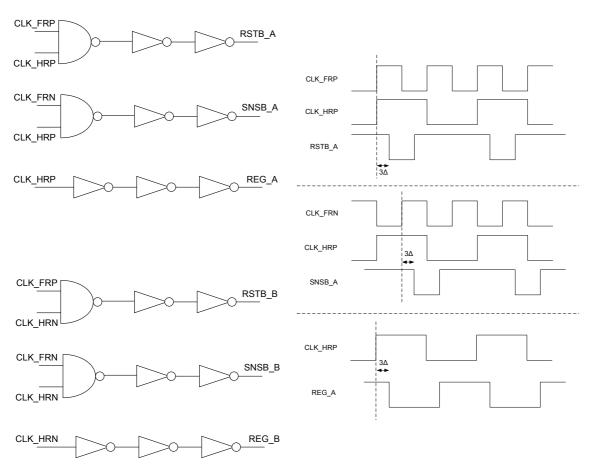

| 3.4.5        | Full-rate clocks signals generation  |  |

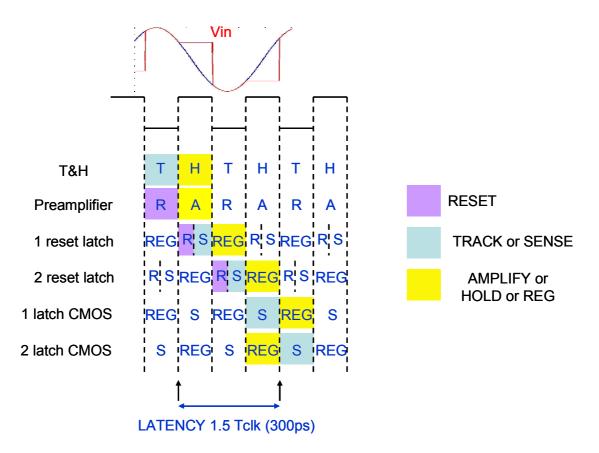

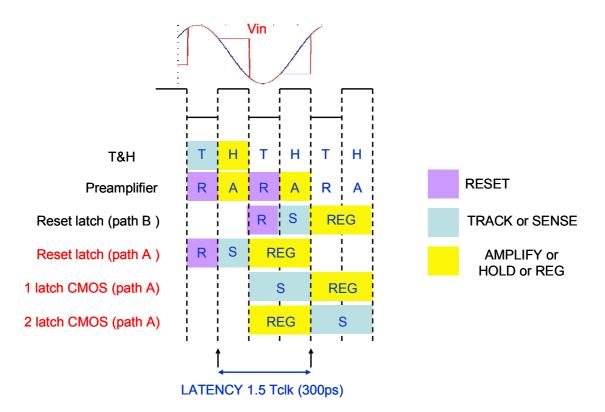

| 3.4.6        | Full-rate timing diagram             |  |

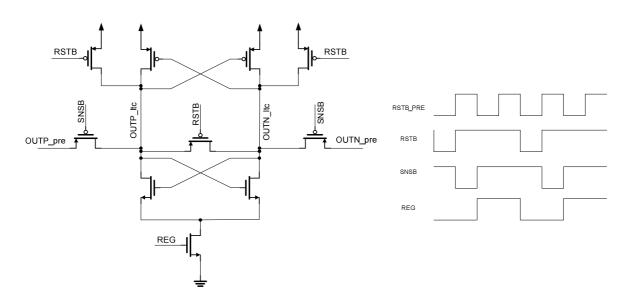

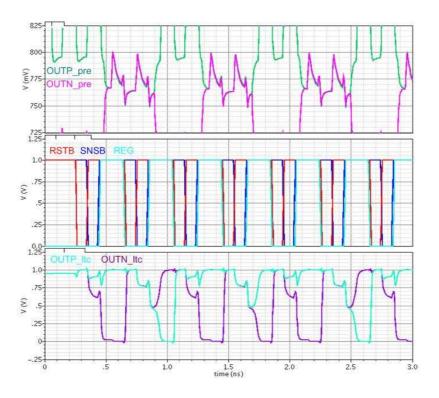

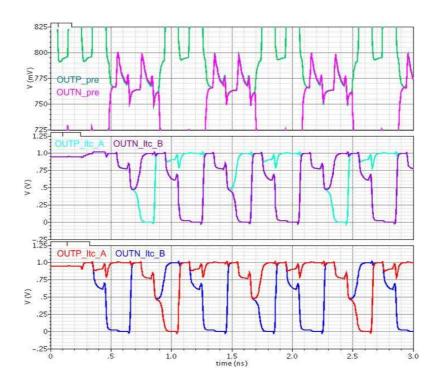

| 3.4.7        | Half-rate latches                    |  |

| 3.4.8        | Half-rate clock signals generation   |  |

| 3.4.9        | Half-rate timing diagram             |  |

| 3.4.1        | 0 Power consumption comparison       |  |

| 3.5          | OFFSET CALIBRATON                    |  |

| 3.5.1        | Introduction                         |  |

| 3.5.2        | Auto-zero                            |  |

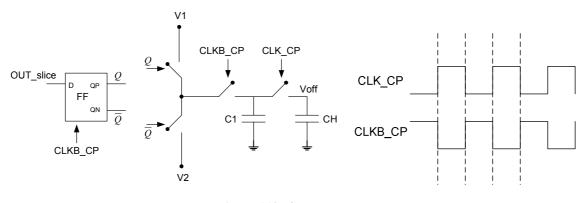

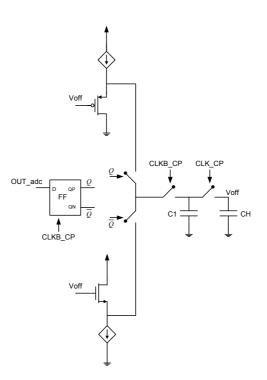

| 3.5.3        | Charge pump                          |  |

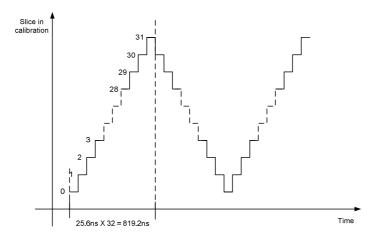

| 3.5.4        | Algorithm                            |  |

| 3.5.5        | Digital signals generation           |  |

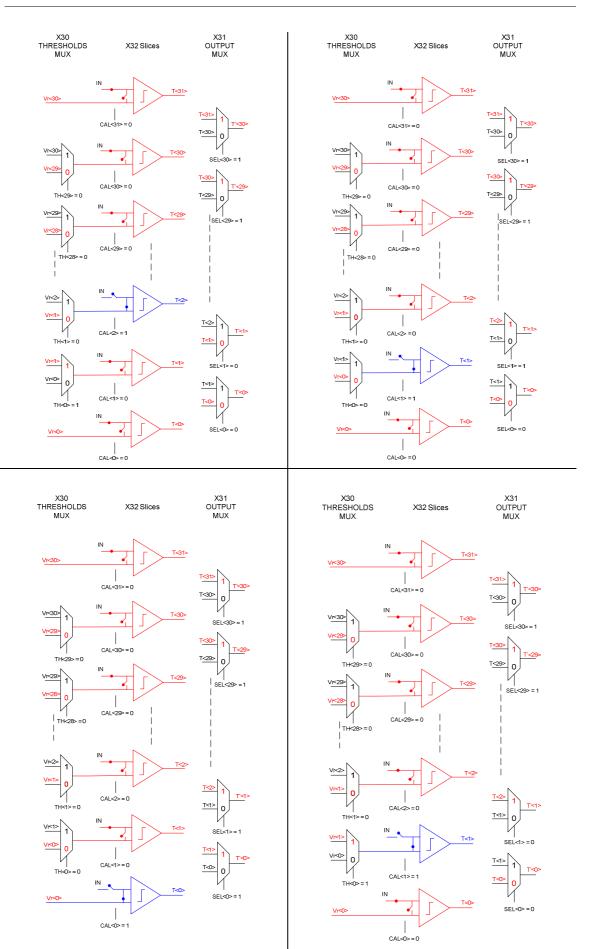

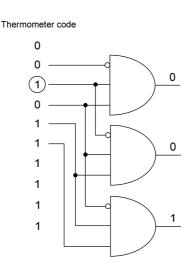

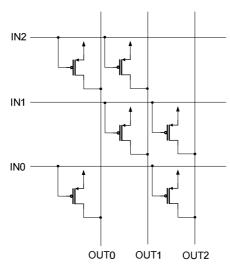

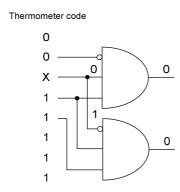

| 3.6          | DIGITAL ENCODING                     |  |

| 3.6.1        | Introduction                         |  |

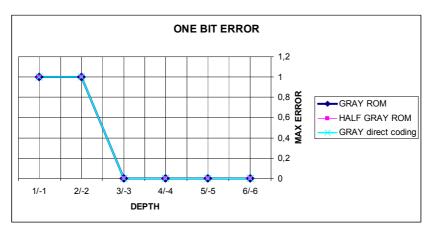

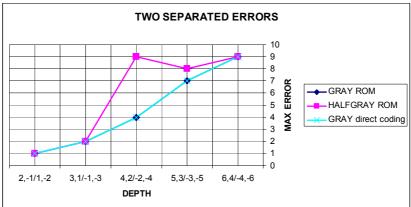

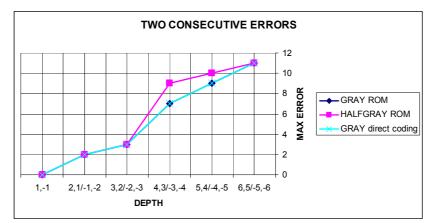

| 3.6.2        | ROM based encoder                    |  |

| 3.6.3        | Gray Direct Coding                   |  |

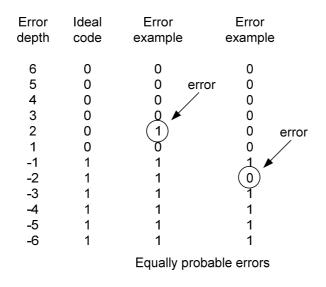

| 3.6.4        | Errors metric                        |  |

| 3.6.5        | Single error remover                 |  |

| 3.6.6        | Errors rejection evaluation          |  |

| 3.6.7        | Digital encoder design               |  |

| 3.7          | ADC SIMULATIONS RESULTS              |  |

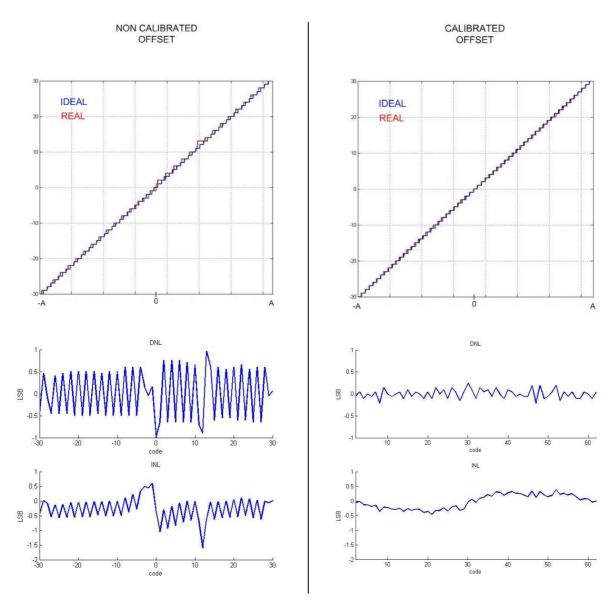

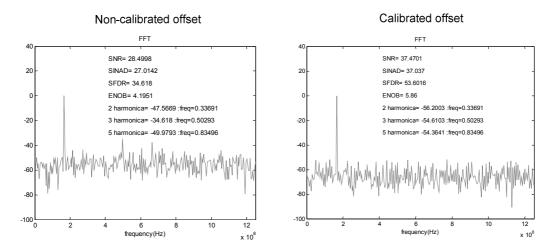

| 3.7.1        | Simulated DNL and INL                |  |

| 3.7.2        | Simulated ENOB                       |  |

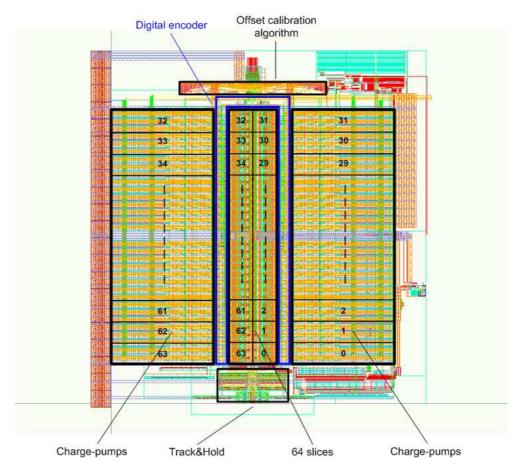

| 3.8          | ADC LAYOUT                           |  |

| 3.9          | LITERATURE COMPARISON                |  |

| 3.10         | SUMMARY                              |  |

| CONCLUS      | SIONS                                |  |

| REFERENCES 1 |                                      |  |

Data rates in serial communications have been steadily increasing with on-chip processing rate and logic density both in network applications and in hard-disk interconnects. The data rates are now exceeding 10Gbits/second (Gb/s). A widely used approach is based on continuous-time or discrete-time forward (FFE) and feedback (DFE) equalizers. This analog approach shows its limits with the increase of the data rates resulting to be completely not adequate for certain specific high-demand applications (optical links and high cross-talk links).

A common trend has been the increasing use of digital signal processing. There has been a growing interest in incorporating CMOS analog-to-digital converters (ADCs) as the frontend of high-speed serializers/deserializers (SerDes). By quantizing the signal with an ADC, the digital signal representation enables greater flexibility and more powerful signal processing techniques to achieve lower bit-error rates (BER), ease of programmability and extensibility for different channel characteristics, and robustness to process variations.

This thesis focuses on both the analog and digital approaches. In particular we describe the digital circuits of an analog receiver and a high speed flash ADC which can be used as front end in a digital receiver.

In chapter one an overview of the main characteristics of high-speed serial communication is presented. First of all, the signal modulations, used in this type of communication (NRZ and RZ), and the serial link standards are analyzed. After, we describe the main system metrics and the source of non-idealities that limit the performances. The analog and the digital equalization approaches are described and finally, clock and data recovery (CDR) architectures are analyzed both for analog and digital receiver.

In chapter two we describe an analog receiver for a 12 Gb/s data rate. Data equalization is based on a linear equalizer (LE) followed by a continuous-time DFE (CTDFE). The chapter analyzes in detail the digital circuits that have been designed: a digital bangbang CDR, the circuits to auto-adapt the CTDFE in order to maximize the equalization efficiency and some auxiliary circuits. Finally we show the measurement results and the literature comparison. This comparison shows that the presented receiver has the better equalization capability between the first in class serial interface receivers, published in the last three years at ISSCC.

In chapter three a 6bit, 5GS/s CMOS flash ADC is described. This ADC can be used as digital front-end of an ADC-based receiver for SerDes applications. The sampling rate of the ADC is the data rate of the SerDes. CMOS ADC implementations have reached multi-GSamples/s (GS/s) sampling rates. Such high sampling rates are typically achieved using a flash ADC architecture. To exceed 10GS/s, multiple ADCs are time-interleaved using multiple clock phases.

We first define the specifications of each flash ADC block. After, we perform a comparison between two flash ADC architectures and we select the better one in terms of power consumption. We also describe the digital encoder, which converts the thermometer output in a binary format and the digital algorithm for the offset calibration. Finally simulated results are shown. Measured results are not available because the ADC is not yet been integrated. The tape-out is planned in mid-november 2010. The partials simulated results show that the designed ADC is comparable with the best-in-class 6 bit ADCs in terms of energy consumption per conversion step.

## Chapter 1

## **HIGH SPEED SERIAL LINK**

#### **1.1 INTRODUCTION**

In this chapter we analyze the main characteristics of high-speed serial communication. First of all we analyze the signal modulations used in this type of communication (NRZ and RZ) and the serial link standards, referring both to copper links and optical links. After, we describe the main system metrics and the sources of non-idealities limiting the system performances.

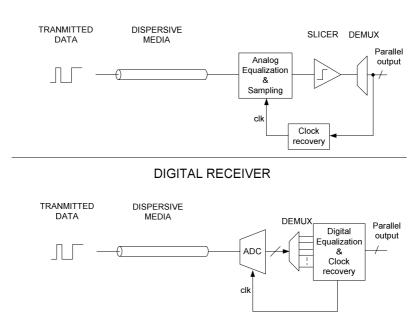

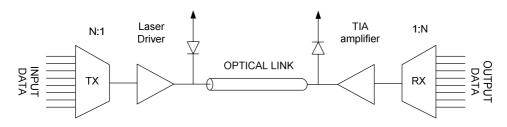

We also analyze the analog and digital signal equalization techniques. An analog system is usually based on analog equalization of the transmitted distorted data, and on the detection of the signal zero crossing by a slicer. On the contrary, the digital approach is based on analog to digital conversion of the input distorted signal, and equalization in the digital domain. A digital equalization is not always based on the signal zero crossing detection. In both approaches, a clock recovery circuit is necessary to recover the correct sampling clock, used for reading the received signal. The last part of this chapter deals with clock recovery circuits for both analog and digital receivers. The serial received signal, correctly recognized, is de-multiplexed and made available in a parallel form, as shown in Figure 1. A digital receiver is able to correctly equalize some kind of data links (such as the multimode optical ones) which an analog receiver is not able to equalize. We focus on analog and digital receivers because the next chapters deal with circuit blocks for both of them. Chapter two describes the digital circuits used in an analog receiver. Chapter three focuses on the design of a flash ADC, which can be used as the front-end for a digital receiver.

ANALOG RECEIVER

Figure 1: Analog and digital receivers.

#### **1.2 BINARY CODING**

Most serial communication systems employ simple binary amplitude modulation of the signal for easy of detection.

A random binary sequence consists of logical ONEs and ZEROs that carry the information and usually occur with equal probability.

#### 1.2.1 NRZ data

In "Non return to zero" (NRZ) coding the logical symbols (ONE and ZERO) are simply represented by high or low voltage (or current) signals, with a duration of a bit period Tb. We refer also to the bit period with the term unit-interval (UI)

The bit rate is equal to 1/Tb per second. It is important to note that the bit stream does not give explicit information on Tb value. A pure random data stream may contain arbitrarily long strings of the same logic value (also called "runs") exhibiting a local low "transition density".

These strings create difficulties in particular operation as clock recovery. For this reason, communication standards specify the maximum "run length" as the maximum number of consecutive ONEs or ZEROs.

It is also interesting to examine a random binary data p(t) in the frequency domain assuming that the single bit is simply a rectangular pulse of width Tb.

In this case the power spectral density is given by:

**1.1**

$$S_x(f) = \frac{1}{Tb} |P(f)|^2$$

Where P(f) represents the Fourier transform of p(t):

**1.2**

$$P(f) = Tb \cdot \frac{\sin(\pi \cdot f \cdot Tb)}{\pi \cdot f \cdot Tb}$$

And so the spectrum of a random sequence is expressed as:

**1.3**

$$S_x(f) = Tb \cdot \left[\frac{\sin(\pi \cdot f \cdot Tb)}{\pi \cdot f \cdot Tb}\right]^2$$

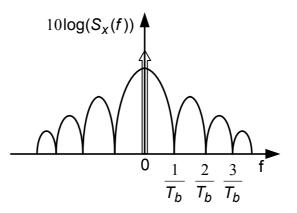

Noting that the  $sin(\pi \cdot f \cdot Tb)$  vanishes at f = n/Tb for integer values of n: this spectrum is shown in Figure 2.

The above analysis yields an important attribute of random binary sequences. For bit rate of 1/Tb the spectrum exhibits no power at frequencies equal to 1/Tb, 2/Tb, etc.

The spectrum exhibits a delta in the zero frequency due to the non-zero mean of the NRZ signal (the considered signal is between zero and one).

This observation proves critical in the task of clock recovery.

Figure 2: Spectrum of a NRZ random sequence.

#### 1.2.2 RZ data

In "return to zero" (RZ) data each bit consist of two sections: the first section assumes a value, that represents the bit value, and the second section is always equal to a logical zero. So that, every two symbol carrying information are separated by a redundant zero symbol.

The RZ signal can be viewed as the product of a NRZ sequence and a periodic square wave. The spectrum of RZ is the convolution of the two spectrums.

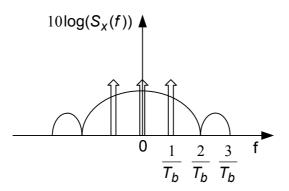

In contrast to NRZ data RZ waveforms exhibit a spectral line at a frequency equal to the bit rate, thereby simplifying the task of clock recovery.

Comparing the spectra of NRZ versus RZ reveals the drawback of RZ: it occupies about twice the bandwidth of NRZ, Figure 3.

Figure 3: Spectrum of RZ random sequence.

#### 1.2.3 Generation of random data

In simulation and characterization, it is difficult to generate completely random binary waveforms because of randomness to manifest itself, the sequence must be very long. For this reason, it is common to employ standard "pseudo random" binary sequences (PRBS).

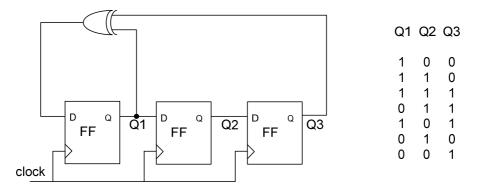

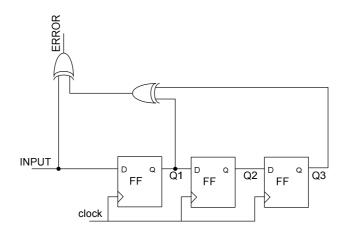

Each PRBS is in fact a repetition of a pattern that itself consist of a random sequence of a number of bits. As an example of PRBS generation consider the circuit shown in Figure 4, where three flip flop form a shift register and a XOR gate senses Q1 and Q3, returning the result to the input of the first flip flop.

In that figure the flip flop outputs are also indicated: the generated pattern repeats every  $2^3-1 = 7$  clock cycles. We also note that if the initial condition is 000, the register remains in a degenerate state; thus some means of initialization is necessary. The waveform produced by the above circuit is an example of a relatively random sequence. One attribute of randomness is "dc balance": the total number of ONEs in each period

differs from that of ZEROs by only one; note also that the maximum run length is equal to three. Other properties of the PRBSs are described in [1].

Figure 4: PRBS generator.

This technique can be extended to an m-bits system so as to produce a sequence of length  $2^{m}$ -1. For example many serial communication circuits are tested with a PRBS of length  $2^{7}$ -1,  $2^{15}$ -1,  $2^{23}$ -1,  $2^{31}$ -1, with a maximum run length of 7, 15, 23 and 31 respectively.

It is important to note that the spectrum of pseudo-random data sequences is quite different from that of really random data sequence. Since the random pattern is repeated periodically, we expect the spectrum to contain only impulses.

Its shape is similar to the really random data one but consists of only spectral line appearing at integer multiple of  $[(2^{m}-1)Tb]^{-1}$ . Of course, for long random pattern, the impulses are very closely spaced, creating an almost continuous spectrum.

The correctness of the data stream, generated through a PRBS, can be tested through a PRBS checker. Figure 5 shows the checker for the PRBS 3 shown in Figure 4: we perform a logical XOR between the input data, generated by the PRBS, and the Q1 XOR Q3 gate output. This signal is called ERROR. If the received sequence is correct the ERROR signal is zero. Moreover ERROR signal is right only after receiving at least 3 bit. The main advantage in using a PRBS data stream is that the generated sequence is self-aligning. This means that the sequence correctness can be verified without the need to find an align sequence.

Figure 5: PRBS checker.

## **1.3** LINK OVERVIEW

For over 20 years, the parallel bus interface has been the mainstream storage interconnects for most storage systems [2]. Increasing bandwidth and flexibility demands have exposed inefficiencies in the two main parallel interface technologies: SCSI (Small Computer System Interface) and ATA (Advanced Technology Attachment). The lack of compatibility between parallel ATA and SCSI increases costs for inventory management, R&D, training and product qualification. Continued demands for higher speeds, more robust data integrity, smaller designs and wider standardization cast doubt on the ability of parallel technology to economically keep pace with increasing CPU processing power and disk drive speeds.

In addition, shrinking budgets are making it increasingly difficult to sustain the costs of developing and managing multiple backplane types, validating multiple interfaces and stocking multiple I/O connections.

Terminating parallel signals is also difficult, requiring individual lines to be terminated, usually by the last drive, to avoid signal reflection at the end of a cable.

Finally, parallel's large cable and connector size make it unsuitable for increasingly dense computing environments.

A possible way to avoid this constrain is in a serial solution.

This technology draws its name from the way it transmits signals, that is, in a single stream (serially) compared with the multiple streams found in parallel technology.

Serial technology wraps many bits of data into packets and then transfers the packets up to 30 times faster than parallel down the wire to or from the host.

#### 1.3.1 Link description

The system's physical layer defines the passive interconnect, the transmitter and receiver device electrical characteristics.

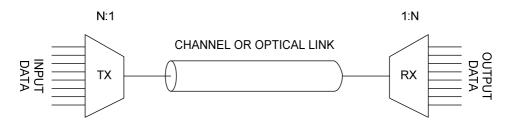

A general serial data link, valid for all the described standards, is shown in Figure 6. The input data are provided to the transmitter in a parallel form, they are multiplexed and transmitted in a serial form through a copper link or an optical link; the transmitted data are so received by a receiver and converted in a parallel form, the output data.

Figure 6: Generic serial data link.

#### 1.3.2 Serial channel link

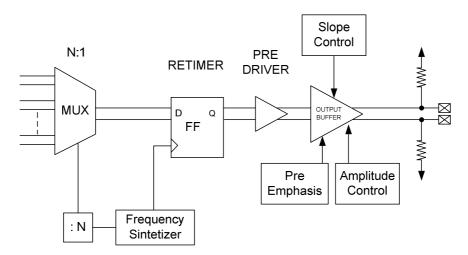

The goals of a transmitter for high-speed communication system are to convert an incoming parallel data stream to a serial data stream and send it to the receiver, with the appropriate slope and amplitude, through a channel [3]. For this reason, often the transmitter is called serializer.

A general block diagram is presented in Figure 7.

Figure 7: Transmitter block diagram.

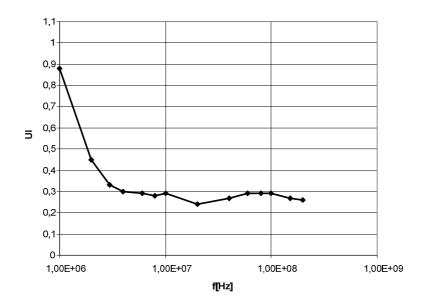

Increasing the data rate up to several Gb/s over cables of several meters or long on-chip interconnects, the propagation of the signal is affected by non-idealities due to circuit performance, limited channel's bandwidth and reflection.

The attenuation of cable increases with cable length and frequency. Therefore preemphasis techniques in the transmitters have been adopted to compensate for the intersymbol interference (ISI) distortions.

Traditional interconnect design required numerous data pins, address pins, control signal and clocking signals. These bus based designs could provide point to multipoint interconnections but as the number of devices connected to a bus increased, so did the associate capacitance, reducing achievable data rate.

Recent trends in high-speed system interconnect concentrates on reducing the pin count, increasing the overall throughput and decreasing complexity and cost. To obtain the highest data throughput while reducing the pin count or data bus width, the clock frequency must be increased. Increasing the clock frequency makes the channel more sensitive to the capacitive loading effects, including reflections as would be experienced by adding multiple drop nodes on the interconnect, and crosstalk, caused by poor electrical interface [4].

Moreover long, high-speed pc-board traces operate in a zone influenced by both skineffect and dielectric losses. Both mechanisms attenuate the high-frequency portion of your signals but in slightly different ways. The skin effect is the tendency of current flow in a conductor to be confined to a layer in the conductor close to its outer surface. As frequency is increased the depth to which the current flow can penetrate is reduced according to skin depth:

**1.4** SKIN\_DEPTH =

$$\sqrt{\frac{2\rho}{\omega\mu}}$$

Where  $\mu$  is the product of  $\mu$ r (relative permeability) and  $\mu$ 0 (vacuum permeability),  $\rho$  is the conductor resistivity (ohm\*meters) and  $\omega$  is the frequency (rad/s).

Consequently we can see that the apparent resistance of a line increases with frequency:

**1.5**

$$R(\omega) = \frac{\rho}{SKIN\_DEPTH} \left(\frac{L}{\pi D}\right)$$

where L and D are the line's sizes.

The dielectric losses too are related to the media characteristic. Each media is characterized by a dielectric constant  $\varepsilon$ ; this constant is the product between  $\varepsilon 0$ , the vacuum dielectric constants (expressed in F/m), and  $\varepsilon r$  the **relative** dielectric constants. Dielectric loss tangent (Tan $\delta$ ) is the ratio between the imaginary and the real part of the dielectric constant and determines the losses of the media.

**1.6**

$$\tan(\delta) = -\frac{\varepsilon_{im}}{\varepsilon_{real}} = \frac{\sigma}{\omega\varepsilon}$$

Both the skin-effect and the dielectric-loss effect degrade digital signals in the same fundamental way, by smearing the rising and falling edges. The difference is that dielectric attenuation varies directly with frequency, and skin-effect attenuation varies only in proportion to the square root of frequency. Moreover, in backplane as well as in integrated circuit environments, a premium on space and costs precludes creating completely shielded links. Therefore, moving to faster data rates, high frequency signal components couple more electromagnetic energy into neighboring channels.

This coupling manifests as near-end crosstalk (NEXT) and far-end crosstalk (FEXT).

NEXT is interference between two pairs of a cable measured at the same end of the cable as the transmitter; FEXT is interference between two pairs of a cable measured at the other end of the cable from the transmitter.

The channel attenuation increases with frequency, while near-end crosstalk grows up very fast with frequency and at high frequency becomes wider than received signal.

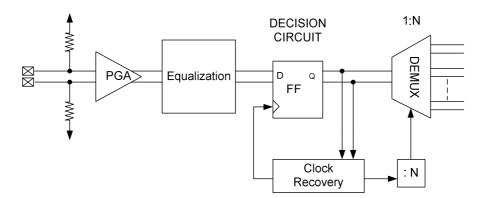

The receiver must detect the input signal and its clock, conditioning the signal itself to maximize the effectiveness of the decision circuit.

Finally the receiver converts the serial data received in a parallel flow and sends it to the logic core. Generic receiver architecture is shown in Figure 8.

Figure 8: Receiver block diagram.

There is an input matching network followed by a programmable gain amplifier (PGA). The PGA regulates the input data swing, different for each standard, to match the optimal one for the following stages. The received data, amplitude adapted, must be equalized to correctly recognize it.

There are several ways to perform this: an analog equalization, a digital equalization or a mixed mode one. An analog equalization is usually based on a linear equalizer with adaptable boost and peak frequency followed by a decision feedback equalizer (DFE), while a digital equalization is based on an ADC and a successive digital signal processing. The equalized data is correctly recognized by a decision circuit and then demuxed by a demultiplexer (so the receiver is called de-serializer and the join of transmitter and receiver is called SerDes).

To properly recover the data, the best sampling phase must be chosen and this task is called clock recovery (CR).

### 1.3.3 Serial channel link standard

The serial links described in this section are: Serial Attached SCSI (SAS), Serial ATA (SATA) and Fiber Channel. SAS is an evolution of parallel SCSI into a point-to-point serial peripheral interface in which controllers are linked directly to disk drives. SAS is a performance improvement over traditional SCSI because SAS enables multiple devices (up to 128) of different sizes and types to be connected simultaneously with thinner and longer cables ; its full-duplex signal transmission supports up to 3.0Gb/s. In addition, SAS drives can be hot-plugged.

SATA extends the ATA technology roadmap by delivering disk interconnect speeds starting at 1.5 Gb/s, moving up to 3, 6 and maybe 12 Gb/s in the next future. Due to its lower cost per gigabyte, SATA will continue as the prevalent disk interface technology in desktop PCs, sub-entry servers and networked storage systems where cost is a primary concern.

An important Serial ATA standard characteristic is Spread Spectrum Clocking (SSC), used to improve the EMI performance of the interface. It takes the form of frequency modulation (FM) of the data clock. This has the effect of spreading the radiated energy across more of the frequency spectrum and lowering the power at any one frequency. SSC also reduces the likelihood that your device will interfere with the operation of some other piece of equipment. The parameters that describe FM are deviation and rate; the standard considers a deep of 5000 ppm and a frequency of 30 kHz. Applying a FM, we are varying the frequency of our signal and the period and the position of our edges. Conversely, the varying edge position claims more challenging during the receiver design.

Fiber Channel (FC) is a technology for transmitting data between computer devices at high data rates. Also Fiber Channel, thanks to his speed, has begun to replace the SCSI as the transmission interface between servers and clustered storage devices. Fiber channel electrical signals are sent over a duplex differential interface. The link may consist of electrical transmission lines such as coaxial cable and shielded twisted pair or two optical fibers. The serial data stream is independent of the transmission medium used; the pattern of ones and zeros is exactly the same whether bits are sent by means of light or electrical signals.

The fiber channel standard is described in the optical link standards section more in depth.

#### 1.3.4 Serial optical link

The idea of using light as a carrier for signal has been around for more than a century, but it was not until the mid 1950s that researches demonstrate the utility of the optical fiber as a medium for light propagation.

A simple optical communication system consists of three components: an electrooptical transducer, for example a laser diode, which converts the electrical data to optical form; a fiber which caries the light produced by the laser (the optical link); and a photodetector, for example a photodiode, which senses the light at the end of the fiber and converts it to an electrical signal. With long or low cost fiber, the light experience considerable attenuation as it travels. Thus the laser must produce a high light intensity, the photodiode must exhibit a high sensitivity to light and the electrical signal generated by the photodiode must be amplified with low noise.

These observation lead to the system shown in Figure 9: a laser driver deliver a large current to the laser and a transimpedance amplifier (TIA) amplifies the photodiode output with low noise and sufficient bandwidth, converting it to a voltage.

Figure 9: Optical link.

The transmitter and the receiver are equal to the ones described in the preceding paragraph, without the output and input matching network.

The optical fiber consists of a core that carries the light from the transmitter to the receiver; surrounding the core is another layer called the cladding, its function is to confine the light to the core and prevent it from escaping the fiber. The cladding accomplishes this by taking advantage of an optical phenomenon that occurs when light encounters a boundary between two medium with different transmission characteristics: the reflection.

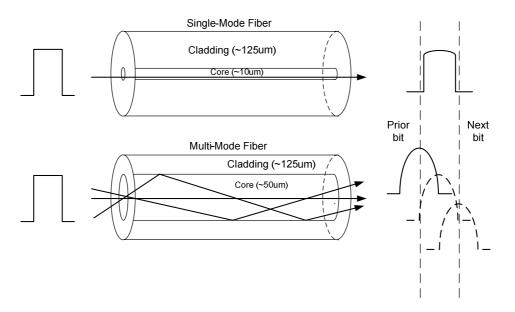

Optical fiber can be categorized as either single mode fiber or multimode fiber based upon the manner in which the light propagates through the fiber. In single-mode fiber, all the light propagates along the same path in the fiber. This is accomplished by reducing the diameter of the core to such a degree that all the light is constrained to follow the same path (the core diameter is approximately 9um).

In multimode fiber, the core diameter is much larger (approximately 50um) resulting in multiple propagation modes, or path, that the light can follow, Figure 10. This results in a phenomena called modal dispersion. Modal dispersion results in spreading of the pulse and ultimately limits the distance and data rate that can be achieved with multimode fiber.

Figure 10: Single-mode and Multimode propagation.

Optical fiber provides several distinct advantages over copper transmission lines that make it very attractive medium for many applications. Among those advantages are:

- Greater distance capability than is generally possible with copper at the same data rate;

- Insensitive to induced electromagnetic interference (EMI);

- No emitted electromagnetic radiation (RFI);

- No electrical connection between the two ports;

- Not susceptible to crosstalk;

- Compact and lightweight cables and connectors.

On the other hand, optical link have some drawbacks:

- Optical links tend to be more expensive than copper links over short distances;

- Optical connector don't lend themselves to backplane printed circuit wiring;

- Optical connector may be affected by dirt and other contamination.

#### 1.3.5 Serial optical link standard

Fibre channel is an example of serial optical link standard [5].

Fibre channel is a technology for transmitting data between computer devices at data rates up to 8.5 Gbit/s, compatible with lower data rate as 1.0625 Gbit/s, 2.125 Gbit/s, 4.25 Gbit/s

This allows different products and configurations to use different signalling rates as appropriate.

Fibre Channel defines multiple optical variants using both single-mode and multimode optical fibers. The purpose in defining multiple options is to allow for flexibility in making cost versus performance trade-offs for different applications.

Using multimode optical fiber the information is sent for a maximum distance of 500m.

Using single-mode optical fiber the information can be sent for a maximum distances in excess of 50 km between a transmitter and a receiver. This distance can be extended even further by using repeaters or proprietary links.

Optical data transmission is accomplished by using electrical signals to control an optical emitter such as a LASER diode. The resultant optical pulses are injected into a fiber optic cable.

Within the fiber optic cable, light pulses are carried via a glass strand approximately the diameter of a human hair. At the receiver end of the optical fiber, the optical pulses are converted back into electrical signals by use of a photo detector.

While it is possible to send signals in both directions simultaneously through a single optical fiber, it is generally simpler and more cost effective (at least for computer interfaces) to use two separate fibers, one carrying information in each direction.

Using two fibers also makes it easier to convert between optical and electrical media because it is not practical to send electrical signals in both directions simultaneously through a single electrical transmission line.

## **1.4 System Characterization**

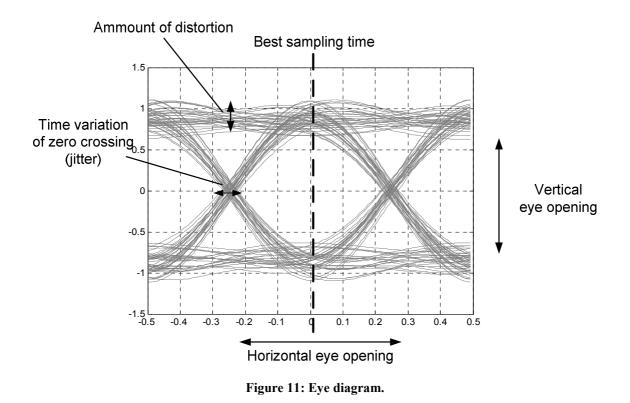

## 1.4.1 Eye diagram

The eye diagram is a useful tool for the qualitative analysis of signal used in digital transmission. It provides at-a-glance evaluation of system performance and can offer insight into the nature of channel imperfections [7].

Careful analysis of this visual display can give the user a first-order approximation of signal-to-noise, clock timing jitter and skew.

The eye diagram is an oscilloscope display of a digital signal, repetitively sampled to get a good representation of its behaviour: It is a composite view of all the bit periods (UI) of a captured waveform superimposed upon each other.

The eye diagram can be used to examine signal integrity in a purely digital system: such as fiber optic transmission, network cables or on a circuit board.

A good use of the eye diagram is to evaluate the received signal quality. The diagram in Figure 11 illustrates the type of information that can be determined from the eye diagram.

#### 1.4.2 Bit error ratio (BER)

Bit error rate, BER is a key parameter that is used in assessing systems that transmit digital data from one location to another. Systems for which bit error rate is applicable include radio data links as well as fibre optic data systems, Ethernet, or any system that transmits data over a network of some form where noise, interference, and phase jitter may cause degradation of the digital signal.

As the name implies, a bit error rate is defined as the rate at which errors occur in a transmission system.

The definition of bit error rate can be translated into a simple formula:

**1.7**

$$BER = \frac{Number of errors}{Total number of bits sent}$$

Typical BER values in data storage application are  $10^{-12}$  or  $10^{-15}$ . In some applications, called error-free, the BER must be  $10^{-17}$ .

#### 1.4.3 Bathtub curves

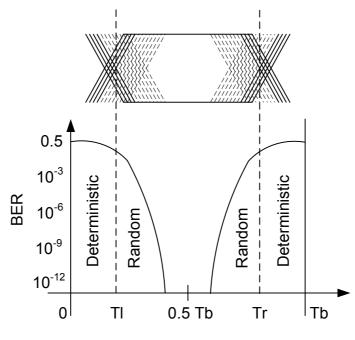

A bathtub curve is a graph of BER versus sampling point throughout the Unit Interval, Figure 12.

Figure 12: Bathtub plot.

It is so named because its characteristic curve looks like the cross-section of a bathtub.

A bathtub plot is typically shown with a log scale that illustrates the functional relationship between sampling time and BER [8].

When the sampling point is at or near the transition points, the BER is 0.5: equal probability for success or failure of a bit transmission. The curve is fairly flat in these regions, which are dominated by deterministic jitter phenomena.

As the sampling point moves inward from both ends of the unit interval, the BER drops off precipitously. These regions are dominated by random-jitter phenomena and the BER is determined by the sigma of the Gaussian processes producing the random jitter. As one would expect, the center of the unit interval provides the optimum sampling point.

#### *1.4.4 Jitter tolerance*

Serial data communication embeds the clock signal in its transmitting data bit stream. At the receiver side, this clock needs to be recovered through a clock recovery (CR) device where phase-locked loop (PLL) circuits are commonly used. It is well known that a PLL typically has certain frequency response characteristics. Therefore, when a receiver uses the recovered clock to time or retime the received data, the jitter seen by the receiver follows certain frequency response functions.

The clock recovery circuit typically has a low-pass frequency response function with a pole at f=fc. This suggests that a receiver can track more low-frequency jitter at frequencies of f < fc than at higher frequencies of f > fc.

Jitter tolerance is defined as the maximum jitter amplitude, typically sinusoidal jitter, in the input data stream of a receiver not producing errors or synchronization anomalies. The jitter amplitude corresponds with the closure of the incoming data's eye.

The sinusoidal jitter's amounts at different frequencies are often specified by the recommendations in the form of masks.

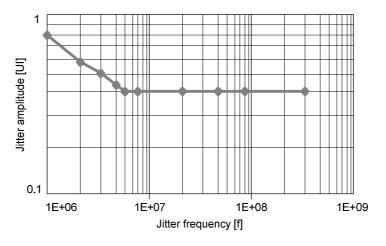

In Figure 13 is shown an example of jitter tolerance: the jitter amplitude is specified in UI versus frequency.

Jitter tolerance is used to define a specific about the "strength" of the receiver.

Figure 13: Jitter tolerance.

## **1.5 PERFORMANCES LIMITS**

The serial link performances (the ability to correctly recognize the transmitted data) are limited by a number of non idealities.

The channel bandwidth limitation or the modal dispersion of an optical fiber introduces intersymbol interference (ISI) in the binary data and so deteriorate the detection of data, degrading both the amplitude and the time resolution.

The noise of the receiver can also significantly impact the detection of the data and affect, like the channel bandwidth limitation, both horizontal and vertical eye opening.

#### 1.5.1 Intersymbol Interference (ISI)

Intersymbol interference is a form of distortion of a signal in which one symbol interferes with subsequent and preceding symbols. This is an unwanted phenomenon as the subsequent and preceding symbols have similar effect as noise, thus making the communication less reliable. ISI is usually caused by bandlimited channels or multipath propagation causing successive symbols to "mix" together. The presence of ISI in the

system introduces errors in the decision device at the receiver output. Therefore, in the design of the transmitting and receiving filters, the objective is to minimize the effects of ISI, and thereby deliver the digital data to its destination with the smallest error rate possible.

A communication link is usually characterized by its frequency response (of low pass type) and its impulse response.

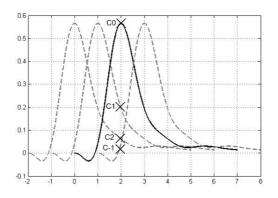

Figure 14 shows a generic impulse response of a cable with bandwidth limitation: C0 is called the cursor and normally represent the maximum amplitude of the pulse, C1, C2 ecc. are called post-cursor and represent the pulse amplitudes at distances multiples of the bit duration (Tb) after the cursor, C-1 is called the pre-cursor and is the pulse amplitude at a distance Tb before the cursor.

If a series of bits are sent through a channel the time response of the individual bits can be summed with the correct time shift due to the time invariance of the transmission medium.

Figure 15 shows this behaviour: if the current bit is considered in the sampling instant, the value is given by the sum of the current cursor plus the preceding bits post-cursors and the subsequent bit pre-cursor.

Figure 14: Channel impulse response.

Figure 15: ISI in a bandlimited channel.

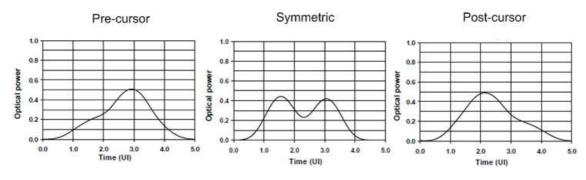

The pulses response of a multimode optical fiber can have a different shape with respect to the cable tipical one shown in Figure 14. This behaviour is due to the modal dispersion.

The pulse response can present a big pre-cursor, a symmetric shape with a pre and post cursor bigger than the cursor or a big post-cursor. Figure 16 shows these types of impulse response in a multimodal fiber as defined by the IEEE 802.3aq 10GBASE-LRM standard [6].

Figure 16: Optical pulses shape.

#### 1.5.2 Noise

Random data propagation through a cable or optical link may experience considerable attenuation. Thus the noise at the receiver can significantly impact the detection of the data. Since noise directly trades with gain, bandwidth and power dissipation of the receiver circuits, it is important to determine how much noise can be tolerated for given performances. The data bits must ideally be sampled by the clock at their midpoint so as to provide maximum distance from the decision. It's possible to derive the error rate in terms of the additive noise amplitude.

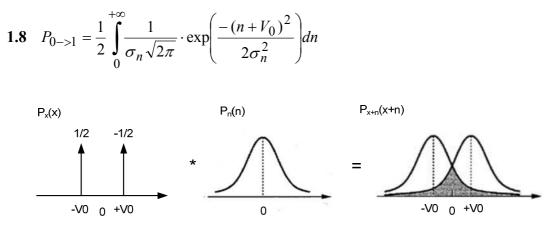

If the binary sequences toggle between  $-V_0$  and  $V_0$  with equal probabilities its probability density function (PDF) is Px(x) and consists of two impulses at  $-V_0$  and  $V_0$ , each having a weight of 1/2; the PDF of the noise n(t) is Pn(n) and exhibits a Gaussian distribution with zero mean and RMS value  $\sigma_n$ .

We can see that the PDF of the signal + noise, Figure 17, is the convolution of the two PDF and consist of two Gaussian distribution centered around  $-V_0$  and  $V_0$ , the shaded tails represent samples of  $-V_0 + n(t)$  that are positive and samples of  $V_0 + n(t)$  that are negative.

We must now calculate the probability of error: the probability that the actual bit is a logical ZERO but the received level  $-V_0 + n(t)$  is positive is given by the shaded area in Figure 17 from 0 to  $+\infty$ :

Figure 17: PDF of the signal + noise.

If ONEs and ZEROs arrive with equal probabilities and the noise corrupts high and low levels equally than  $P_{0->1} = P_{1->0}$  and we need calculate only one and multiply by two this result to obtain the total probability:

**1.9**

$$P_{TOT} = Q\left(\frac{V_0}{\sigma_n}\right)$$

Where Q(x) is the Q function defined as:

1.10

$$Q(x) = \int_{x}^{+\infty} \frac{1}{\sqrt{2\pi}} \cdot \exp\left(\frac{-u^2}{2}\right) du$$

How can we expect the BER decrease as the  $V_0/\,\sigma_n$  increase.

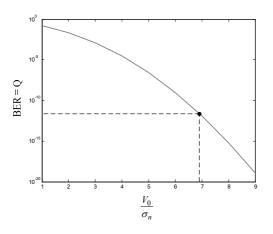

Figure 18 shows the BER versus  $V_0/\sigma_n$ . If we want a BER of  $10^{-12}$ , the ratio between half the signal range and the noise standard deviation must be at least equal to 7.

Figure 18: BER versus  $V_0/\sigma_n$ .

#### 1.5.3 Jitter

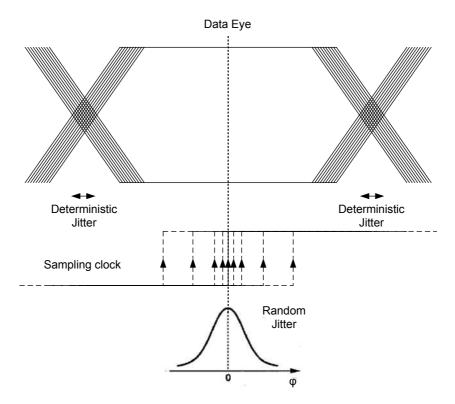

Jitter is the deviation of the zero crossing from their ideal position in a signal (clock or data). The goal of the receiver is to sample the incoming signal at the data center in order to maximize the eye opening. Both the clock and data jitter deteriorate the horizontal eye opening.

In the analysis of serial data system, it's useful to distinguish two categories of jitter: random jitter and deterministic jitter.

The deterministic jitter is mainly due to ISI caused by the transmission media, Duty Cycle Distortion (DCD) in the transmitted data, and Periodic Jitter caused by cross-coupling or EMI problem. The deterministic jitter is referred to the data.

This jitter reduces the horizontal eye diagram by a limited amount and for this reason is said to be bounded.

The random jitter arises from phase noise random processes typically found in VCO structures or clock sources. VCO phase noise varies the period of oscillation randomly as if the oscillator occasionally operates at frequencies different from its nominal and the zero crossing may not occur at integer of the period. In general all the circuit noise is a cause of random jitter. The random jitter is referred to the clock.

The Probability Density Function (PDF) of the random jitter follows a Gaussian distribution and is said to be un-bounded, Figure 19.

Figure 19: Deterministic and Random jitter.

The peak-to-peak value depends on the observation time and its standard deviation is commonly used to describe its magnitude.

## **1.6 ANALOG EQUALIZATION TECHNIQUES**

#### 1.6.1 Introduction

The two main sources of signal distortion in a digital communication channels are ISI and additive noise. The ISI is due to bandlimited channels or multipath propagation and can be characterized by the channel transfer function in the frequency domain or by the impulse response, in the time domain.

The noise can be internal to the system or external to the system; if the noise is introduced primarily by electronic components and amplifiers at the receiver, it may be characterized as thermal noise.

Hence at the receiver the distortion must be compensated in order to reconstruct the transmitted symbols. This process of suppressing channel induced distortion is called channel equalization.

An analog equalization approach uses usually a linear equalizer followed by a DFE (decision feedback equalizer).

### 1.6.2 Linear equalizer

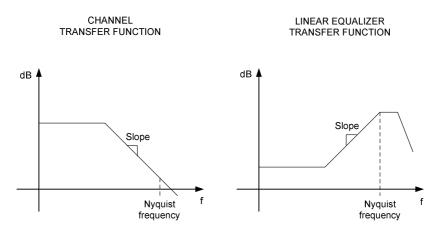

A possible solution of the channel induced ISI problem is to compensate or reduce it with a high-pass filter called equalizer. The channel is a band-limited transmission media of low-pass type.

From the communication theory it is well know that the optimum receiver can be realized as a filter matching the inverse of the channel transfer function in the frequency domain, followed by a sampler operating at the symbol rate [9]. In a digital communication system the channel frequency response is not known with sufficient precision to design optimum filter.

Time-continuous analog filters are extensively employed in systems for analog processing of high-frequency signals. These circuits synthesize the requested transfer function in analogic way.

In order to obtain a high pass filter transfer function, a number of zeros must be introduced at low frequency adequate to match the channel shape, Figure 20.

The equalizer boost is usually placed at the Nyquist frequency, half the data rate one. This frequency is a good compromise because the signal power spectral density is mainly contained under this frequency and the high frequency noise contributions are not too amplified.

Figure 20: Channel and linear equalizer transfer function.

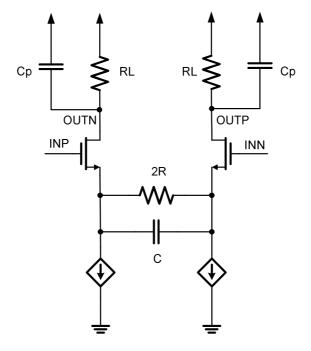

The described transfer function can be obtained using the circuit shown in Figure 21. The differential gain voltage can be easily calculated neglecting the finite value of the drain-source resistance.

$$1.11 \quad G = \frac{Vout}{Vin} = \frac{gm}{1 + gmR} \cdot \frac{1 + S2CR}{1 + \left(\frac{S2CR}{1 + gmR}\right)} \cdot \frac{R_L}{1 + SR_LC_P}$$

Cp is the parasitic capacitance of the circuit that loads the equalizer output.

Figure 21: Linear equalizer.

The RC source degeneration introduces a zero-pole couple with the pole at a frequency (1+gmR) higher than the zero. The load resistance RL and the output parasitic capacitance Cp introduce an additional high frequency pole. To obtain the desired boost, the RC value must be chosen as a trade of between the DC gain and the high frequency boost. This corresponds to a compromise between sensitivity, dynamic range, noise and offset tolerance versus the capability to match the channel. In order to increase the boost a chain of degenerated differential pairs can be used.

#### 1.6.3 Decision Feedback equalizer (DFE)

A band limited channel can be described in the time domain by a Finite Impulse Response (FIR) filter with this transfer function, [9]:

$$1.12 \quad S_n = \sum_{i=-N_{pre}}^{N_{post}} C_i B_{n-i}$$

Where  $S_n$  is the analog value of the distorted symbol after the channel at the time n,  $B_x$  is the x-th digital bit value,  $C_x$  is the x-th pre or post cursor value,  $N_{pre}$  and  $N_{post}$  are the number of pre and post cursors of the impulse response.

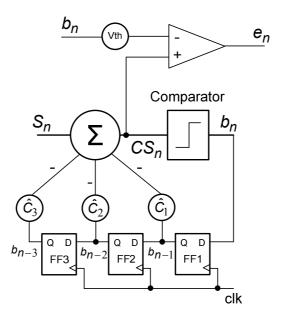

The digital DFE then uses information about previously received bits to cancel out their ISI contributions from the current decision, as shown in Figure 22. This figure shows the block diagram of a 3 taps digital DFE. The shift register clock is a clock at the data rate frequency (full-rate).

Figure 22: 3 taps DFE block diagram.

If the values of the estimated post-cursors  $\hat{C}_1$ ,  $\hat{C}_2$  and  $\hat{C}_3$  are known the circuit removes the ISI of the three previous bits. The DFE can only remove post-cursor ISI. The values of these coefficients are computed through a least mean square algorithm (LMS) that uses the error e(n) signal.

A drawback of DFE implementations is that at high data rates, the latency of the feedback loop in the standard implementation can present a serious bottleneck. The corrections, in fact must be applied in less than one bit time to be effective. The most critical path in term of timing is the one that start at the flip-flops outputs, pass through the post-cursor multiplier, the summer and the comparator and is applied at the first flip-flop input.

The LMS algorithm works is now explained.

3

N<sub>post</sub>

The CS<sub>n</sub> signal is the signal after the ISI correction and can be written in this way:

$$CS_{n} = \sum_{i=-N_{pre}}^{N} C_{i}b_{n-i} - \sum_{i=1}^{N} \hat{C}_{i}b_{n-i}$$

$$CS_{n} = \sum_{i=-N_{pre}}^{0} C_{i}b_{n-i} + \sum_{i=4}^{N_{post}} C_{i}b_{n-i} + \sum_{i=1}^{3} (C_{i} - \hat{C}_{i})b_{n-i}$$

Assuming that the distortion due to the post-cursors after third and to the pre-cursors is negligible, the ISI is corrected.

The signal  $e_n$  is defined as the difference between the equalized signal and the signal called Vth. The Vth must also be computed through the LMS algorithm. In first approximation the Vth will converge to the cursor  $\hat{C}_0$  and for the moment we suppose it is equal to this value.

1.14

$$e_n = CS_n - \hat{C}_0 b_n = \sum_{i=-N_{pre}}^{-1} C_i b_{n-i} + \sum_{i=4}^{N_{post}} C_i b_{n-i} + \sum_{i=0}^{3} (C_i - \hat{C}_i) b_{n-i}$$

Correlating  $e_n$  with the previous bits remains only one term different by zero in terms of mean value.

$$1.15 \quad e_n \cdot b_{n-i} = C_i - \hat{C}_i$$

This is true when the input stream is formed by random data, without correlation between them. The post-cursors estimated values are updated in this way:

**1.16**

$$\hat{C}$$

\_new<sub>i</sub> =  $\hat{C}$ \_old<sub>i</sub> +  $\mu \cdot e_n \cdot b_{n-i}$

$\mu$  is the integral gain of the coefficients update. When the coefficients converge they usually toggle between two values.

The Vth value is also adapted correlating the error with the actual received bit

**1.17**

$$Vth\_new = Vth\_old + \mu \cdot e_n \cdot b_n$$

In a digital implementation of this algorithm it is important to underline that to adapt the coefficients is enough the sign of the error.

#### *1.6.4 Loop-Unrolled digital DFE*

One or more taps of feedback equalization can be achieved by using loop unrolling to avoid the bottleneck in the latency of the feedback loop [10].

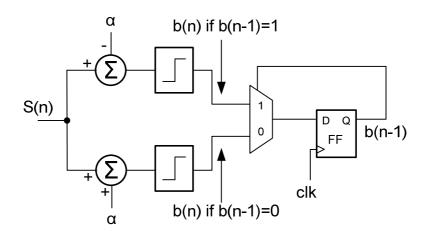

Since we cannot run the feedback loop fast enough, we can unroll it once and make two decisions each cycle. One comparator decides the input as if the previous output was a 1, and the other comparator decides the input as if the previous bit was a 0. Once we know the previous bit, we select the correct comparator output.

Instead of just one data sampler, for binary signaling the receiver has two samplers that are offset by  $\pm \alpha$ , anticipating the impact of trailing ISI  $\alpha$  from a previously sent symbol of value of  $\pm 1$ , Figure 23.

This method can be applied to two or more taps of feedback. To remove N taps of ISI  $2^{N}$  samplers are required, and their offset are all the possible combination of ISI.

Usually, only a small amount of unrolling is needed to bridge the latency gap.

Figure 23: One tap DFE using loop-unrolling.

#### 1.6.5 Half-rate DFE with one tap of loop unrolling

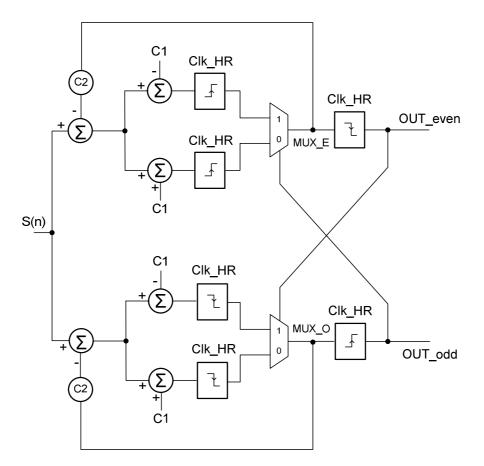

An elegant and efficient DFE architecture that relaxes the timing requirements by a factor of two with respect to the full-rate topology, while still achieving equalization at the maximum data rate, is shown in Figure 24 [11].

This particular DFE employs two techniques to achieve this feat: loop unrolling and half rate clocking. In loop-unrolling decisions are made for both cases in which the previous bit was a "1" and a "0"; this is accomplished by having two analog summers, two regenerative flip-flops, and a mux. The C1 tap now functions as a DC offset and is not dynamically switched. A second flip-flop at the output then drives the mux select, and effectively picks the "correct" decision, thus ignoring the "wrong" decision.

In order to allow 2UI for the critical timing path to settle, a second technique of half rate clocking is employed.

Here, a half-rate clock drives two duplicate paths at opposite clock phases. Decisions "ping-pong" back and forth between the two paths, generates even and odd bit sequences.

Figure 24: DFE architecture employing half-rate clocking and one tap of loop-unrolling.

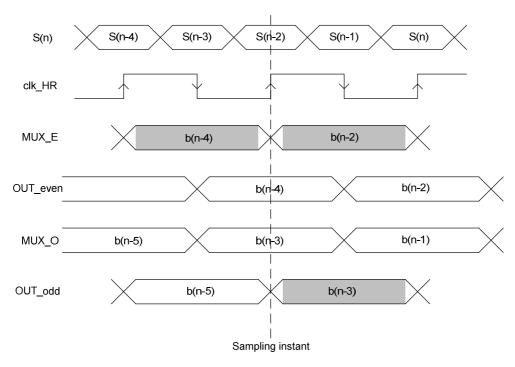

Figure 25 shows the time diagram of this DFE: S(n) is the input signal: the transmitted bits plus the ISI of the successive and previous ones; MUX E signal is the input signal

sampled and corrected on the rising clock edge (only the even bits); MUX\_O signal is the input signal sampled and corrected on the falling clock edge (only the odd bits); OUT\_even and OUT\_odd are the re-sampled even and odd bits.

After the sampling instant, shown in figure, the MUX\_E signal is b(n-2) while before this instant was b(n-4), this value is multiplied by the second post-cursor C2 and subtracted at the input signal. This path, starting at the flip-flops output before the multiplexer, passing through the mux, the C2 multiplier and the two summers, is the critical one but it has 2UI of time to settle.

Figure 25: Half-rate DFE timing diagram.

The even mux selection signal, at the current sampling instant, is instead the odd path output b(n-3).

The same described processing is performed to equalize the odd bits.

In this way both the first and second post-cursor of ISI are correctly subtracted to the input signal.

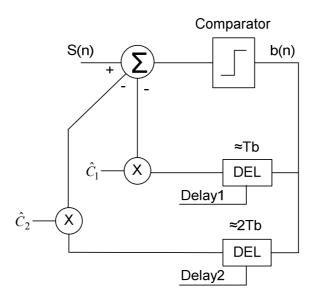

## 1.6.6 Continuous time DFE (CTDFE)

Continuous time or un-clocked architecture is an efficient way to overcome the first feedback loop latency bottleneck exhibited by the conventional digital DFE architecture.

As displayed in Figure 22, digital DFE feeds back binary decisions through a FIR filter, while continuous time decisions are fed back through variable delays approximately equal to multiple of the bit time, [12], [13].

Figure 26 shows an example of a two taps continuous time DFE.

Delays values can be controlled dynamically so that there is an additional freedom degree to maximize the equalization efficiency. The tunable feature also enables dynamic adjustment for changes to the design goal caused by process, voltage and temperature variations.

In the next chapter, we explain an efficient algorithm used to auto-adapt the delay value.

Figure 26: Second order continuous time DFE.

#### **1.7 DIGITAL EQUALIZATION TECHNIQUES**

#### 1.7.1 Introduction

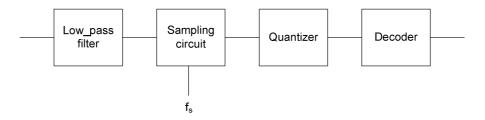

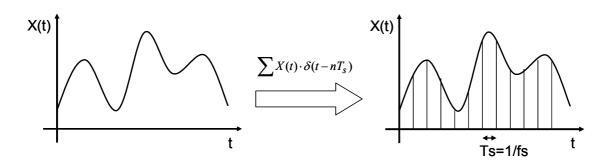

A digital equalization approach is based on the digital conversion through an ADC of the input signal, the transmitted one distorted by the channel, and a successive elaboration focused in the reconstruction of the transmitted bit

The big bottleneck is the power consumption required by the ADC. This converter must be able to sample the incoming signal at the data-rate and convert it with the resolution required by the employed equalization technique.

The digital approach enables power/area scaling with process, simplifies production testing, allows integration of a FFE, and provides a flexible design with a configurable number of filter taps.

The considered digital equalization techniques are two: a digital feed-forward equalizer (FFE) filter and a Viterbi algorithm which is a maximum-likelihood sequence estimator.

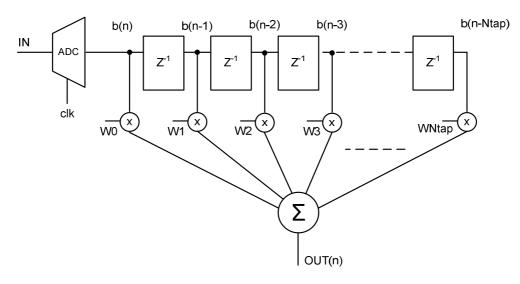

## 1.7.2 Digital Feed-forward equalizer (FFE)

A programmable feed-forward equalizer is usually used as first equalization circuit after the ADC to invert the effect of the channel. The FFE is basically a finite impulse response (FIR) auto-adaptive filter. A FIR filter is a type of a discrete-time filter. The impulse response is finite because it settles to zero in a finite number of sample intervals. This is in contrast to infinite impulse response (IIR) filters, which have internal feedback and may continue to respond indefinitely.

As reported in Figure 27, a FIR filter is formed by a repetition of delay cells, multiplication blocks and adder. Each section, formed by a delay and multiplication pair, is called tap. The output results the sum of the current input with the Ntap previous bits weighted by corresponding coefficients Wi, called tap weight.

$$1.18 \quad OUT_n = \sum_{i=0}^{N_{TAP}} W_i \cdot b_i$$

The impulse response of these filters is defined by the set of tap weights Wi.

Usually an LMS algorithm is used to auto adapt this digital filter setting the taps coefficients in order to have the optimum impulse response that maximizes the eye opening.

Figure 27: FIR filter.

The frequency response of this filter must be of high pass type and perform a boost to match the magnitude of the channel transfer function with reasonable accuracy However, with high losses channels, it is not convenient to boost the signal to much because the ADC quantization noise is also amplified.

For this reason usually the equalized signal, after the FFE, is left with some residual ISI.

In order to equalize further the signal a digital DFE or a Viterbi decoding algorithm is used.

# 1.7.3 VDA (Viterbi decoding algorithm)

In 1967 Andrew Viterbi first presented his now famous algorithm for the decoding of convolutional codes [14]. A few years later, what is now known as the Viterbi decoding algorithm (VDA) was applied to the detection of data signals distorted ISI [15].

In this paragraph we introduce the basic functionality of the VDA without going into details.

A NRZ signal, distorted by a band limited transmission medium, does not show only two possible values (one and zero), but is spread due to ISI over a range of values depending on the number of impulse pre-cursor and post-cursor and on the preceding and subsequent transmitted bits. If the ISI is large it is impossible to recognise the correct transmitted bit by the signal sign. Moreover if the transmitted medium is an optical link and its impulse response presents, for example, a big precursor like the impulses defined in the IEEE 802.3aq 10GBASE- LRM standard [6], a DFE is not adequate to equalize the signal. VDA, instead, is adequate to equalize data link affected by big amount of ISI and also to equalize multimodal fiber data link.

VDA works in this way: we consider a set of possible signal values depending on the number of precursor and post-cursor taken into account. For example if we take into account one pre-cursor and one post-cursor, there are  $2^3$ =8 considered values.

The received signal value is not equal to one in the considered set, because of the additional ISI due to non-considered post-cursors and pre-cursors, but it is possible to find the more similar one. We can define a distance metric between the received value and the values in the considered set; the value in the considered set with the smaller distance respect to the received one is the more similar. The knowledge of this more similar value is not enough to recognize the correct transmitted bit because there are more than one bit sequences that generates that value.

If we know a sequence of at least K received value (where K-1 is the link ISI), it is possible to find the correct value of one bit.

A maximum likelihood algorithm computes the cumulative distance of the received sequence of N values (where N $\geq$ K) with all the possible values corresponding to all the possible bit sequences, and select the more similar one.

Usually the VDA is preceded by an FFE filter that shapes the impulse response to obtain the desired values of pre and post cursors.

The VDA requires an ADC to convert the input signal. The signal value is necessary to compute the distances.

# **1.8 CDR TECHNIQUES**

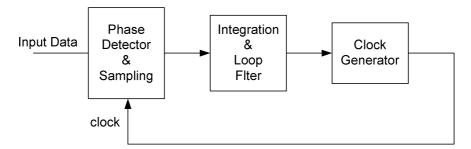

# 1.8.1 Introduction

The data stream received is both asynchronous and noisy. For subsequent processing, timing information a clock must be extracted from the data so as to allow synchronous operation. Furthermore the data must be retimed such that the jitter accumulated during transmission is removed. This task of clock extraction and retiming is called clock and data recovery.

The clock generated must bear a certain phase relationship with respect to data, allowing optimum sampling of the bits by the clock. If the sampling instants coincides with the midpoint of each bit, than the sampling occurs farthest from the preceding and following data transition, providing maximum margin for jitter and other timing uncertainties.

There are two main categories of clock extraction circuits: open loop filters and closed loop synchronizers.

The first solution doesn't suffer from instability and nonlinear problems, but requires high selective external filters and additional calibration to ensure the correct alignment. Conversely, the closed loop CDR is fully integrable and thanks to the loop can self-compensate for changes in the environment.

A closed loop CDR is implemented as shown in Figure 28. A phase detector first recognizes the phase error between the sampling clock and the incoming data, it incorporates also the sampling circuit. After which the error is integrated and this value, passed through a loop filter, is used to generate the sampling clock.

Figure 28: Closed loop CDR.

# 1.8.2 Linear PD (Hogge)

The recovered clock must sample the data in the middle of the eye. In a phase tracking system this is accomplished by measuring the phase difference between the data and the clock and driving it toward the wished value.

The Hogge phase detector is shown in Figure 29.

Since sample B changes only on the clk edges X = Din XOR B contains pulses whose width represents the phase difference between Din and clk.

It is important to note that the circuit produces a pulse for each data transition, thereby providing edge detection, and the width of the output pulses varies linearity with the input phase difference, suggesting that the circuit can operate as a linear PD. This output is called "proportional pulses".

The X output can't be used alone as phase detector because its average value is a function of the transition density and fails to uniquely represent the phase difference for various data patterns.

To overcome the above ambiguity, the proportional pulses must be accompanied by a reference pulses, the Y output. The latter are impulses that appear on data edges but exhibit a constant width, thus eliminating the pattern dependency.

The difference between the areas under X and Y can be viewed as a PD output, eliminating the ambiguity due to transition density.

Figure 29: Hogge phase detector.

The Hogge topology is a true linear phase detector, generating a vanishing average as the phase difference approaches zero.

Usually the Hogge PD output is integrated using a charge pump and the clock is generated through a voltage controlled oscillator (VCO).

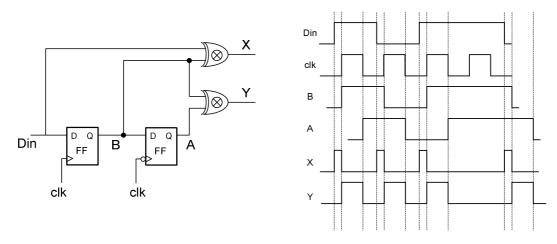

#### 1.8.3 Bang bang PD (Alexander)

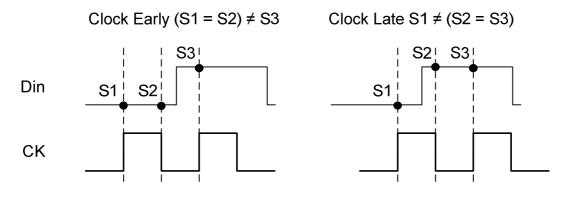

Figure 30 illustrates the Alexander phase detector principle, also known as "early-late" detection method [16]. Using three data samples S1-S3 taken by three consecutive clock edges, the PD can determine whether a data transition is present and whether the clock leads or lag the data. In the absence of data transition, all three samples are equal and no action is taken.

If the clock is early respected to the data, than the last sample S3 is unequal to the first two S1 and S2. Conversely if the clock is late, the last two samples S2 and S3 are equal but unequal to the first sample S1.

Thus S1 XOR S2 and S2 XOR S3 provide the early-late information:

**1.19**

$$\begin{cases} S1 \otimes S2 = 0 \text{ AND } S2 \otimes S3 = 1 \text{ clock } EARLY \\ S1 \otimes S2 = 1 \text{ AND } S2 \otimes S3 = 0 \text{ clock } LATE \\ S1 \otimes S2 = 0 \text{ AND } S2 \otimes S3 = 0 \text{ no Transition} \end{cases}$$

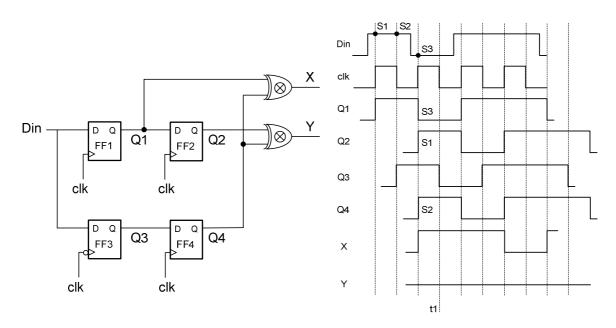

The foregoing observations lead to the circuit topology shown in Figure 31. Flip-flop FF1 samples S1 and S3 on the rising edge of clk and FF2 delays the result by one clock cycle. Flip\_flop FF3 samples S2 on the falling edge of clk and FF4 delays this sample by half a clock cycle.

Figure 30: Alexander PD functioning.

As depicted in Figure 31, the first rising edge of clk samples a high data level. The second rising edge of clk than accomplishes two tasks: it produces a delayed version of the first sample at the output of FF2, and it samples the low level on the input data. On the first falling edge of clk, FF3 samples a high level on the input data and on the next rising edge, FF4 reproduces this level. The values of S1, S2, S3 and S4 are therefore valid for comparison at t=t1. As a result the XOR gates generate valid outputs simultaneously.

The Alexander phase detector is a bang-bang system and the relationship between phase difference and output signals is strongly not linear: the output phase information are only two EARLY or LATE. The CDR loop locks such that S2 coincides with the data zero crossing.

Figure 31: Alexander phase detector.

#### 1.8.4 Mueller Muller PD

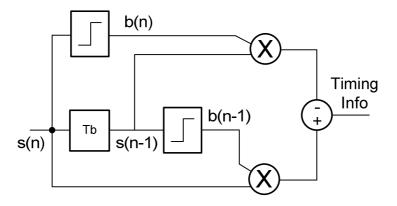

Mueller Muller is an example of a baud rate CDR method and is usually used in a digital receiver where the signal is A/D converted with a clock frequency equal to the symbol rate.

The two phase detecting methods seen before are based on the zero threshold crossing of the received signal, and on the comparison, of this point, with the value sampled on the center of the eye. For this reason, these PD methods are not usually used in digital receiver, where the ADC samples and converts only the signal on the center of the eye.

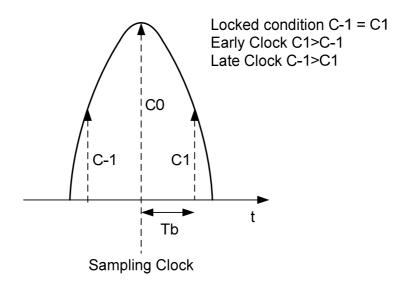

Mueller Muller instead uses the signal derivative at the sampling instant; this derivative, or at least its sign, is usually correlated with the estimated data to produce the updating information required for the timing control loop. The resulting sampling phase is such that the mean square error between the signal and the appropriate reference level is minimized, or, with slight changes, such that the sampling will occur at the peak of the impulse response.

A possible implementation of this algorithm is shown in Figure 32, where s(n) represent the digital converted value at the instant n, and b(n) is its sign.

Correlating s(n) with b(n-1) and subtracting the correlation between s(n-1) and b(n), a phase information is obtained. This information is proportional to the difference between the post-cursor and the pre-cursor of the system impulse response, [17].

**1.20**

$$s(n) \times b(n-1) - s(n-1) \times b(n) \propto (C_1 - C_{-1})$$

Figure 32: Mueller Muller algorithm block diagram.

Mueller Muller can be equivalently seen as an algorithm that sets the sampling clock in the midpoint between two time values. These time values are the ones at which the impulse response amplitude is equal to the estimated first post-cursor and pre-cursor. Figure 33 shows an example of the early-late information generated by supposing a symmetrical impulse response with equal post-cursor and pre-cursor values.

Figure 33: Early-late information in a Mueller Muller algorithm.

## *1.8.5 Clock generation (charge pump & VCO)*

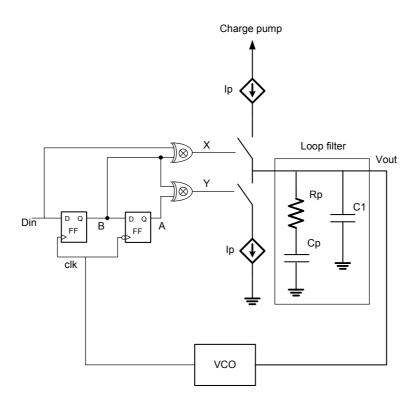

The integrated phase error information must be used to generate the sampling clock. When the error signal is provided from a charge pump followed by an analog filter the most common option is to use a Voltage Controlled Ring Oscillator or LC based VCO. Figure 34 shows a CDR loop incorporating a Hogge PD. The XOR outputs drive a charge pump and a loop filter, the output of the loop filter is the VCO input. The need for a charge pump in linear CDR loops poses serious speed limitations.

Figure 34: CDR based on a Hogge PD, a charge pump and an analog loop filter.

# *1.8.6 Clock generation (phase interpolator)*

When the integrated error is a digital word, coming from a digital filter implemented inside the CDR's loop, solutions based on the UI quantization in time and phase domains, become more practical. This digital approach is used, for example, with Alexander or Mueller Muller PD.

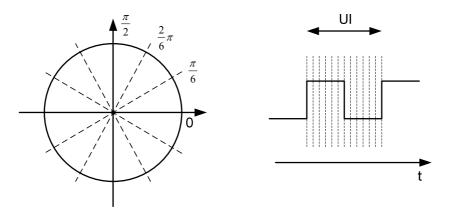

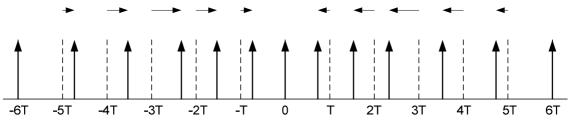

The clock Unit interval is divided in a fixed number of phases and the loop filter output is a digital number representing one phase. Figure 35 shows an example of UI quantization.

Figure 35: Clock unit interval quantization.

A widely used approach, to substitute VCO in digital CDR loop, uses phase interpolator. Given two sine wave, the linear combination of them is again a sine wave, with phase intermediate between the initial ones phases.

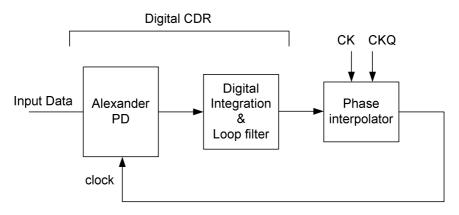

Figure 36 shows the block diagram of a digital CDR and a phase interpolator.

Figure 36: Digital CDR and PI.

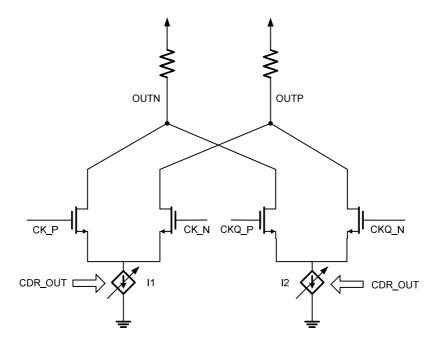

Basically a phase interpolator can be made of two or more differential pairs with programmable tail current I1 and I2, Figure 37. The inputs are two differential reference clocks CK and CKQ. The ratio between the current represents the weight of the two sine waves. Different ratio implies different phase's offset: this ratio is the CDR output.

Figure 37: Phase interpolator.

# **1.9 SUMMARY**

In this chapter we have introduced some concepts about modern communication systems. The most used modulation code (NRZ) and the main data communication standard (SATA, SAS and Fiber Channel) have been analyzed.

We have also described the most important system characterization metrics (eye diagram, BER, bathtub curve and jitter tolerance) and the sources of performance limits (ISI, noise and jitter).

We have analyzed the most important equalization techniques, both analog and digital. The analog ones are: linear equalizer (LE) and different topology of decision feedback equalizer (DFE). The digital ones are: FIR filter (FFE), and the Viterbi decoding algorithm (VDA).

Finally we have described different clock and data recovery (CDR) topologies.

The next chapter deals with a 12 Gb/s receiver and in particular the designed digital circuits.

# Chapter 2

# DIGITAL CIRCUITS FOR A 12GB/S RECEIVER

# **2.1** INTRODUCTION

This chapter focuses on a 12 Gb/s analog receiver for the standards described in the previous chapter. The architecture is based on a continuous-time DFE and on a bang-bang CDR.

The implemented digital circuits are described: a bang-bang CDR for the timing recovery, the circuits implementing the auto-adaptive algorithms for horizontal and vertical eye opening maximization and some auxiliary circuits. Finally the die micrograph, measurements results and literature comparison are shown.

## **2.2 RECEIVER ARCHITECTURE**

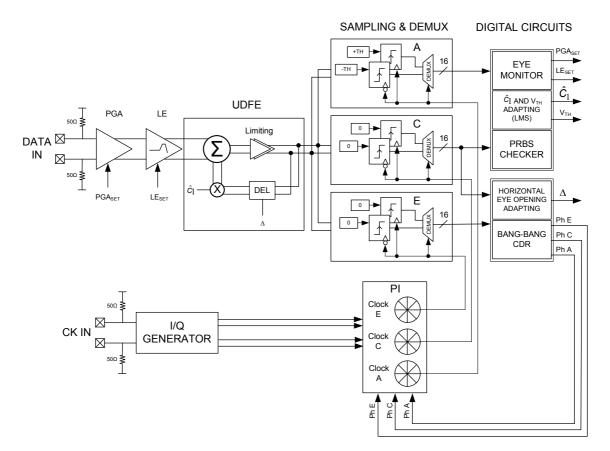

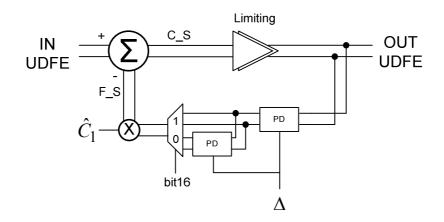

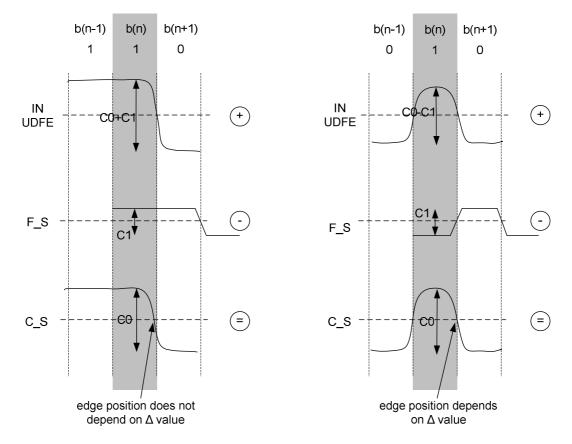

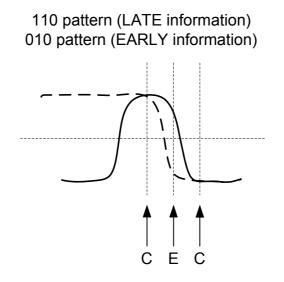

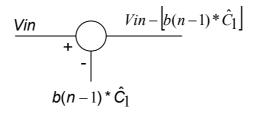

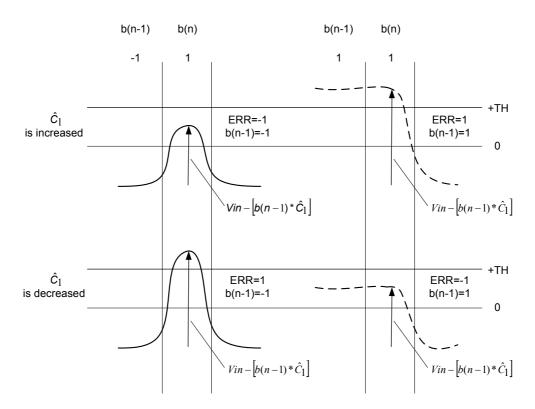

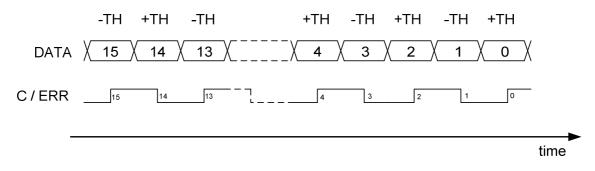

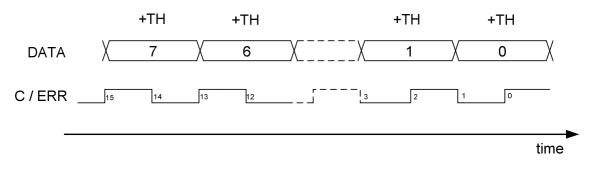

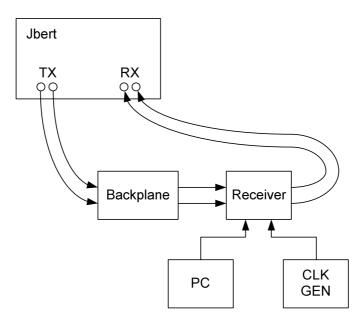

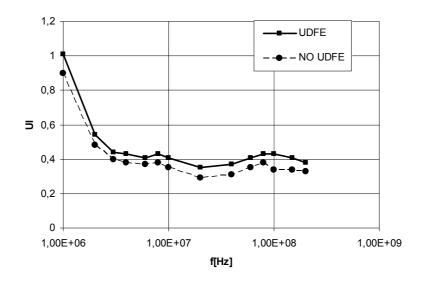

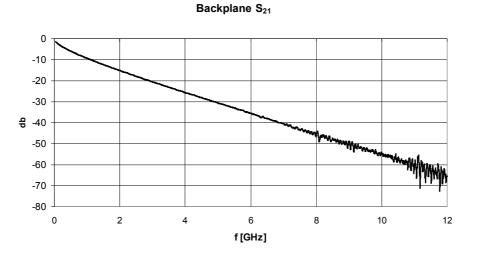

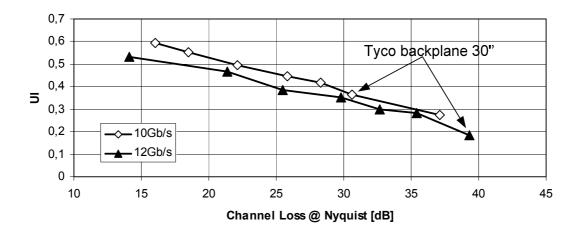

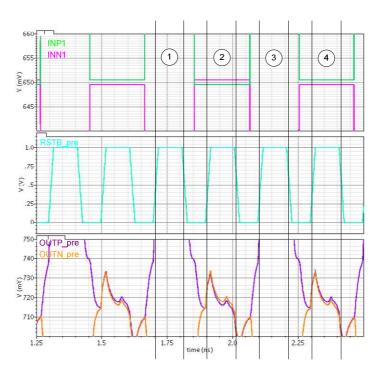

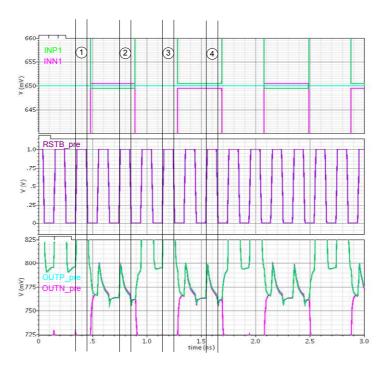

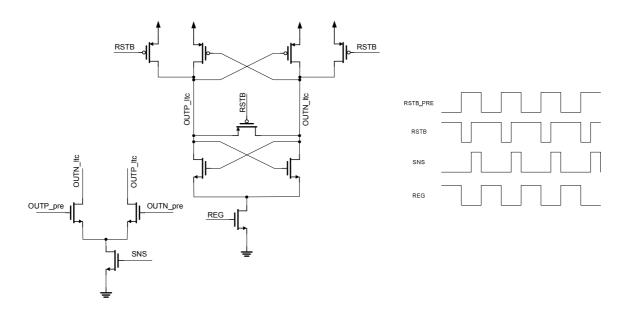

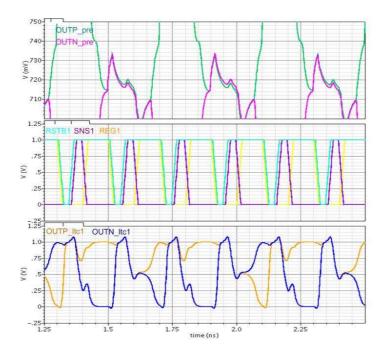

The implemented receiver for a 12 Gb/s maximum data-rate is shown in Figure 38. The NRZ data is provided to a programmable gain amplifier (PGA), that correctly sets the signal amplitude, to a linear equalizer (LE), that partially compensates for the channel induced ISI, and to a continuous time DFE.

The LE pre-shapes the channel pulse-response into a pulse-response with a single dominant post-cursor and this residual post-cursor is removed by the single tap unclocked DFE.

The DFE feedback is composed by a limiting amplifier, a variable delay ( $\Delta$ ) and a multiplier for  $\hat{C}_1$  that represents the residual post-cursor value.

Both the post cursor value  $\hat{C}_1$  and the delay value ( $\Delta$ ) are self-adapted.  $\hat{C}_1$  is computed through an LMS algorithm that maximizes the vertical eye opening;  $\Delta$  is computed through an algorithm capable to concentrate the transitions at the data edge, that optimize the horizontal eye opening.

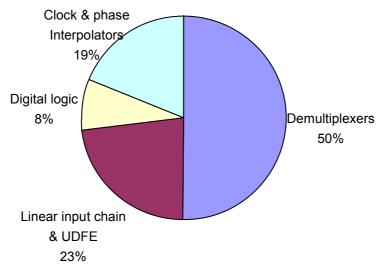

Figure 38: Receiver architecture.

The linear path, made of PGA, LE and unclocked DFE (UDFE), feeds three half-rate sampling paths: center (C), edge (E) and auxiliary (A).

Data through path C are sampled at the center of the eye; data through path E are sampled at data edge. Both of them are demuxed to the bang-bang CDR and to the DFE delay control engine that optimizes the horizontal eye opening.

The auxiliary path A can sample data in variable phase position and respected to programmable thresholds (+/-TH).

Path A can compute the error value of the LMS algorithm to adapt the DFE tap  $\hat{C}_1$ . In this way the LMS algorithm computes also the threshold TH that, in first approximation, is equal to the cursor C0.

Path A can also work as an internal Eye Monitor; this feature is employed to plot the eye diagram at the system start-up and to optimize the PGA and the LE.

The CDR drives three phase interpolators (PI) generating the three sampling clocks.

# 2.3 BANG-BANG CDR

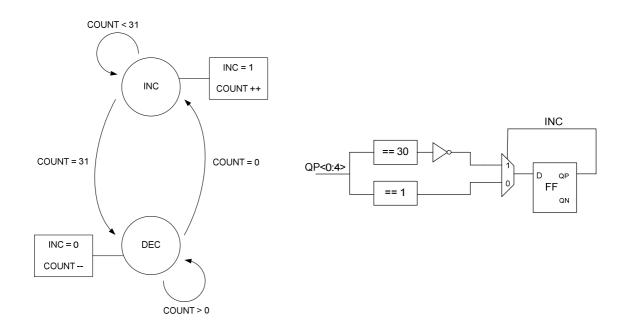

#### 2.3.1 Digital CDR

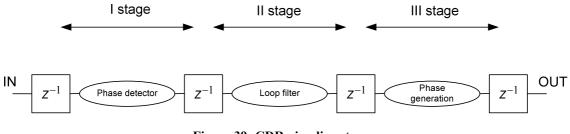

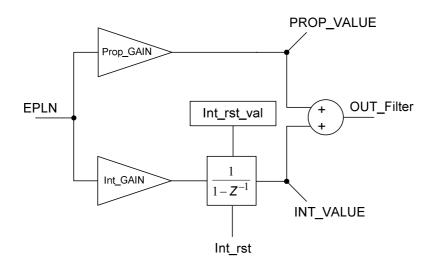

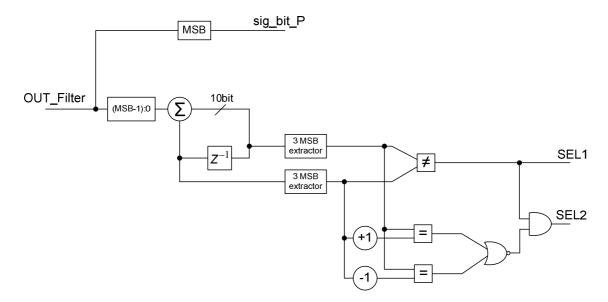

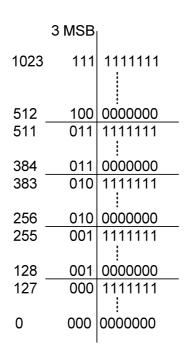

The main issue into designing a digital CDR is to minimizing the latency between input and output and so to minimize the number of pipe-line stage. A digital bang-bang CDR is composed by the phase detector, the loop filter and a digital circuit which generates the representation of the sampling phase, the phase interpolator input. Minimizing the input-output latency, the jitter tolerance is maximized.

We have designed the CDR in only three pipeline stage: the first stage is composed by an Alexander type phase detector, the second stage encloses the proportional-integral loop filter and the third one encloses the phase generation circuit, Figure 39.

Figure 39: CDR pipe-line stages.

The CDR inputs are 16 bits digital words, and its clock has a frequency of 750 MHz. The input output latency is (1/750MHz)\*3 = 4ns. This delay impacts on the CDR bandwidth.

# 2.3.2 Phase detector

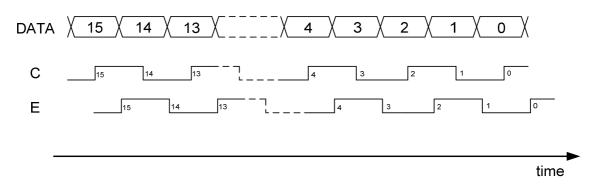

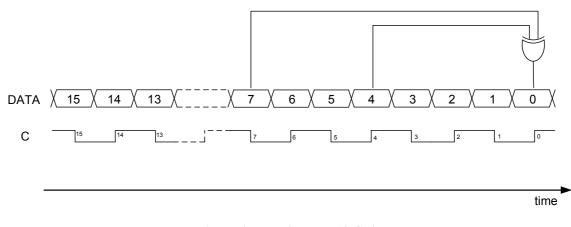

The inputs of the bang-bang CDR are two digital words of 16 bits corresponding to the two demultiplexed sampling paths C and E. The CDR clock frequency is the ratio between 12Ghz (the maximum data-rate) and 16; so the clock frequency is 750Mhz. If not specified, the flip-flops work on the clock rising edge.

The phase detection is performed through an Alexander type phase detector [16] that generates early-late information in parallel.

Figure 40 shows the data, the two clocks used for sampling the data center and the edge, and the notation of all digital circuits. This notation is the "MSB first" one, this means that the most significant bit, the 15<sup>th</sup> one, is the older.

Figure 40: Data and clocks for 12 Gb/s mode.

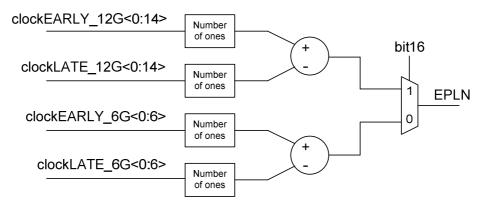

A digital logic computes early-late information in the following way:

$\begin{cases} clock EARLY \_ 12G < n-1 > = \overline{C < n > \oplus E < n >} AND C < n-1 > \oplus E < n > \\ clock LATE \_ 12G < n-1 > = C < n > \oplus E < n > AND \overline{C < n-1 > \oplus E < n >} \end{cases}$

The two vectors contain 15 bits. In both vectors each bit is 1 if there is an early information, zero otherwise.

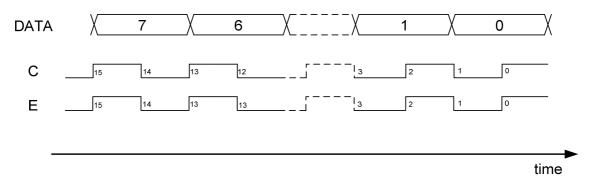

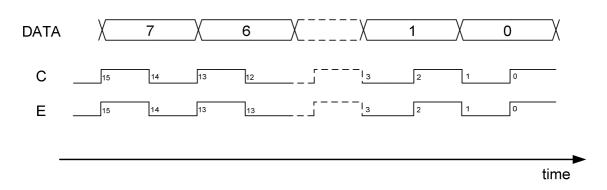

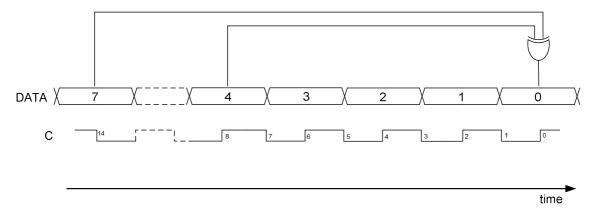

The system is designed for working in the 12Gb/s mode and in the 6Gb/s mode. In the 6Gb/s mode one of the two half-rate paths, that sample data in C, E, and A position, is turned off and clock E is aligned with clock C, Figure 41. In 6Gb/s mode we don't use a 3GHz clock because the phase interpolators are designed to work with 6GHz clock frequency.

Figure 41: Data and clocks for 6 Gb/s mode.

The following logic generates early-late information:

$\begin{cases} clock EARLY _ 6G < n > = \overline{C < 2n + 2 > \oplus E < 2n + 1 >} & AND & C < 2n > \oplus E < 2n + 1 > \\ clock LATE _ 6G < n > = C < 2n + 2 > \oplus E < 2n + 1 > & AND & \overline{C < 2n > \oplus E < 2n + 1 >} \\ \end{cases}$

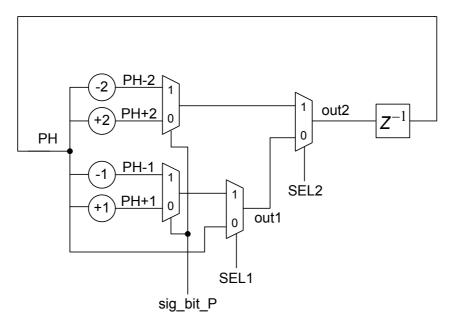

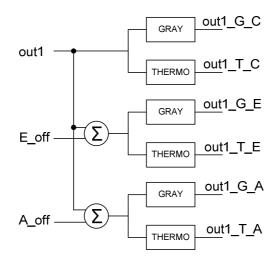

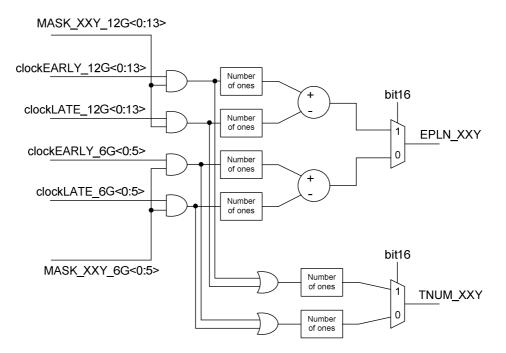

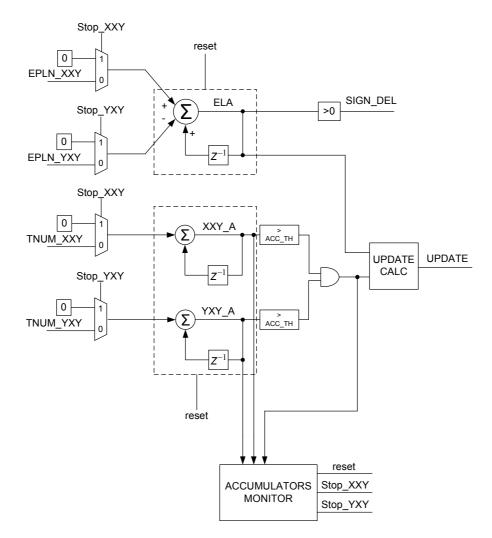

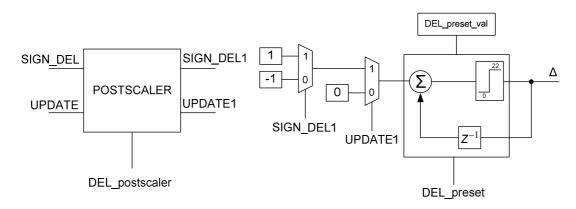

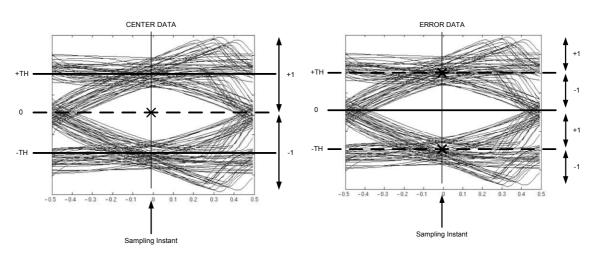

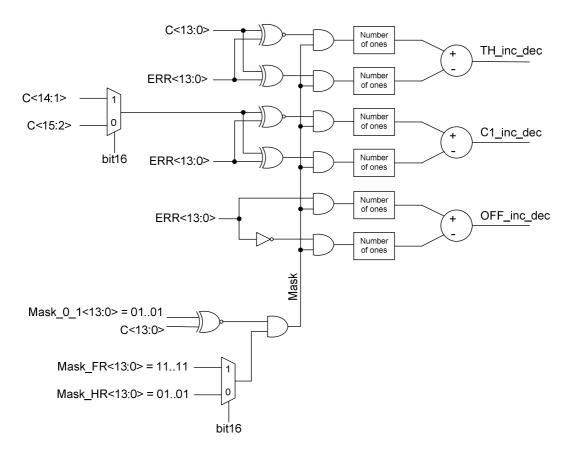

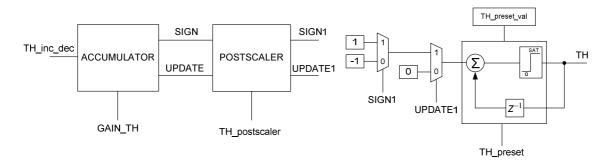

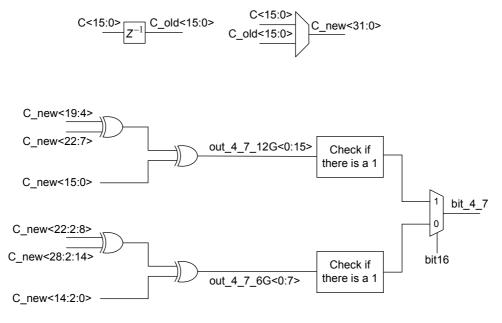

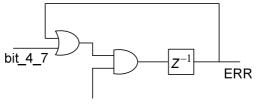

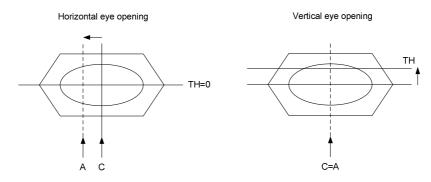

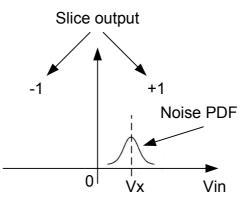

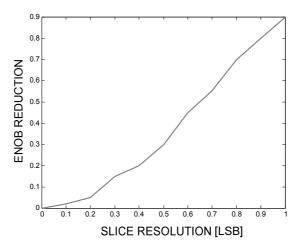

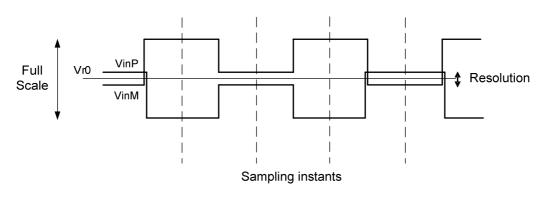

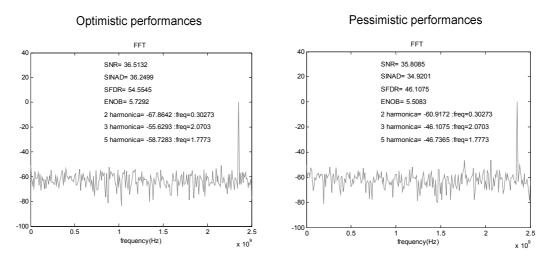

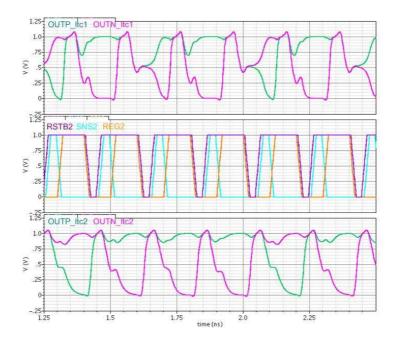

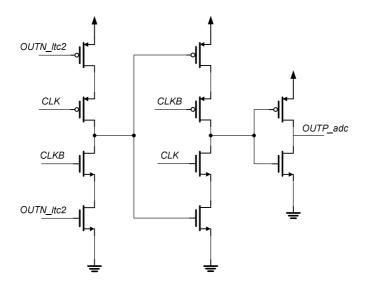

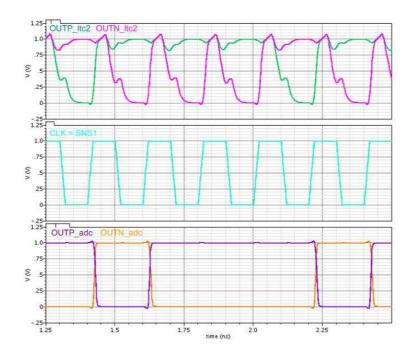

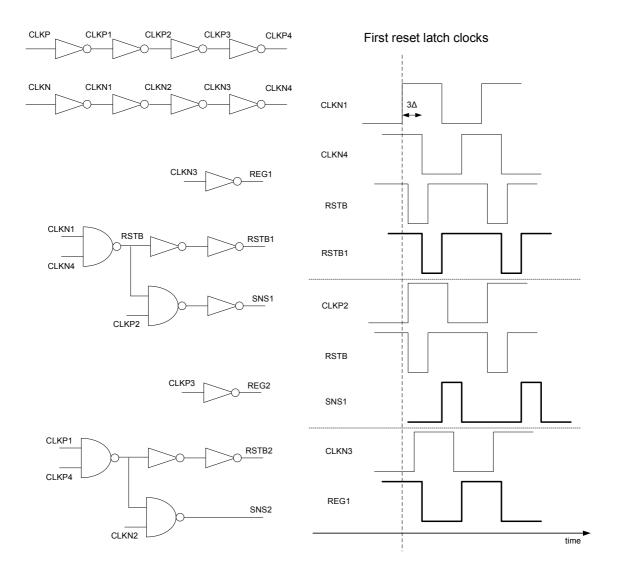

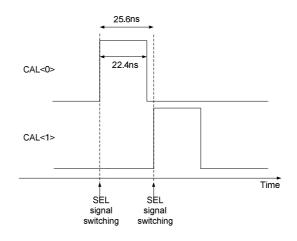

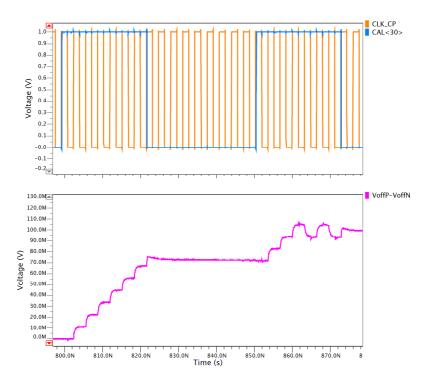

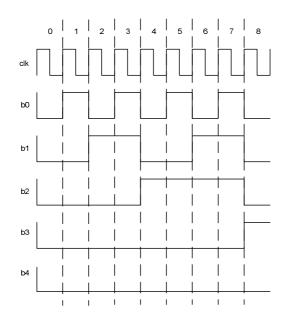

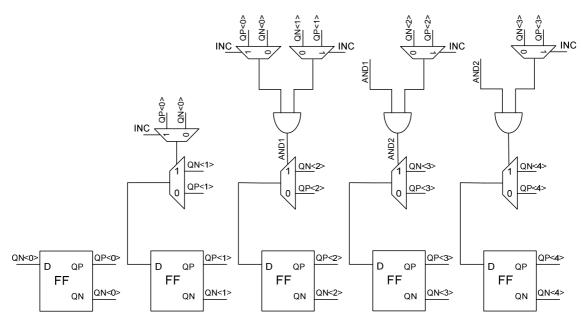

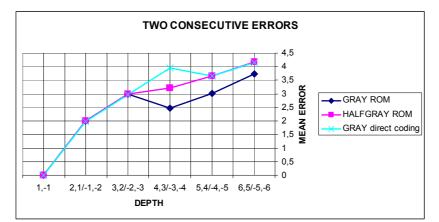

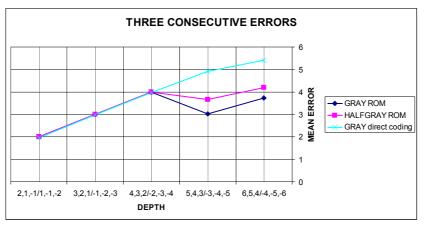

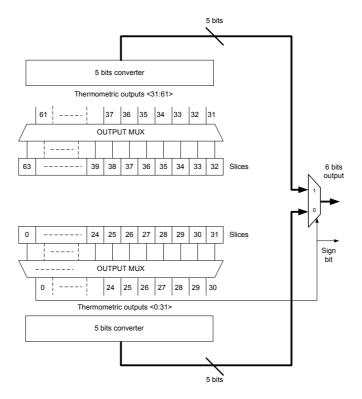

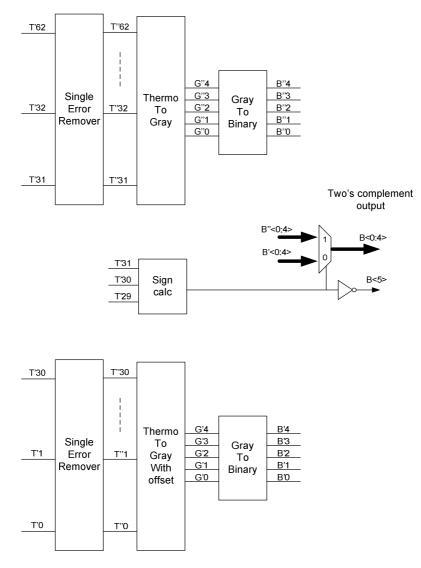

0 ≤ **n** ≤ 6